Tnetx4090 thunderswitch ii, Switch – Texas Instruments THUNDERSWITCH II TNETX4090 User Manual

Page 39

TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

39

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

Table 10. Transmit Pretag Bit Definitions

BIT

NAME

FUNCTION

31–28

reserved

Reserved. These bits always are 0.

27

rxheader

Receive header. Indicates whether an IEEE Std 802.1Q header was added to the frame on reception.

– When rxheader = 1, an IEEE Std 802.1Q header was inserted.

– When rxheader = 0, no IEEE Std 802.1Q header was inserted.

26–25

reserved

Reserved. These bits always are 0.

24–20

portcode

Source port code. Indicates which port on the device received the frame. Codes 00000–01001 indicate ports 0–9,

respectively (port 9 is the NM DIO port). All other codes are reserved and are not generated.

19–17

reserved

Reserved. These bits always are 0.

16–0

xportvector†

Extended destination port vector. A bit for each port on the crossbar matrix. A 1 in position n indicates the frame is

destined for port n on the crossbar matrix.

† Bit vector, in which bit x corresponds to external crossbar matrix port x. Any number of ports can be selected at the same time.

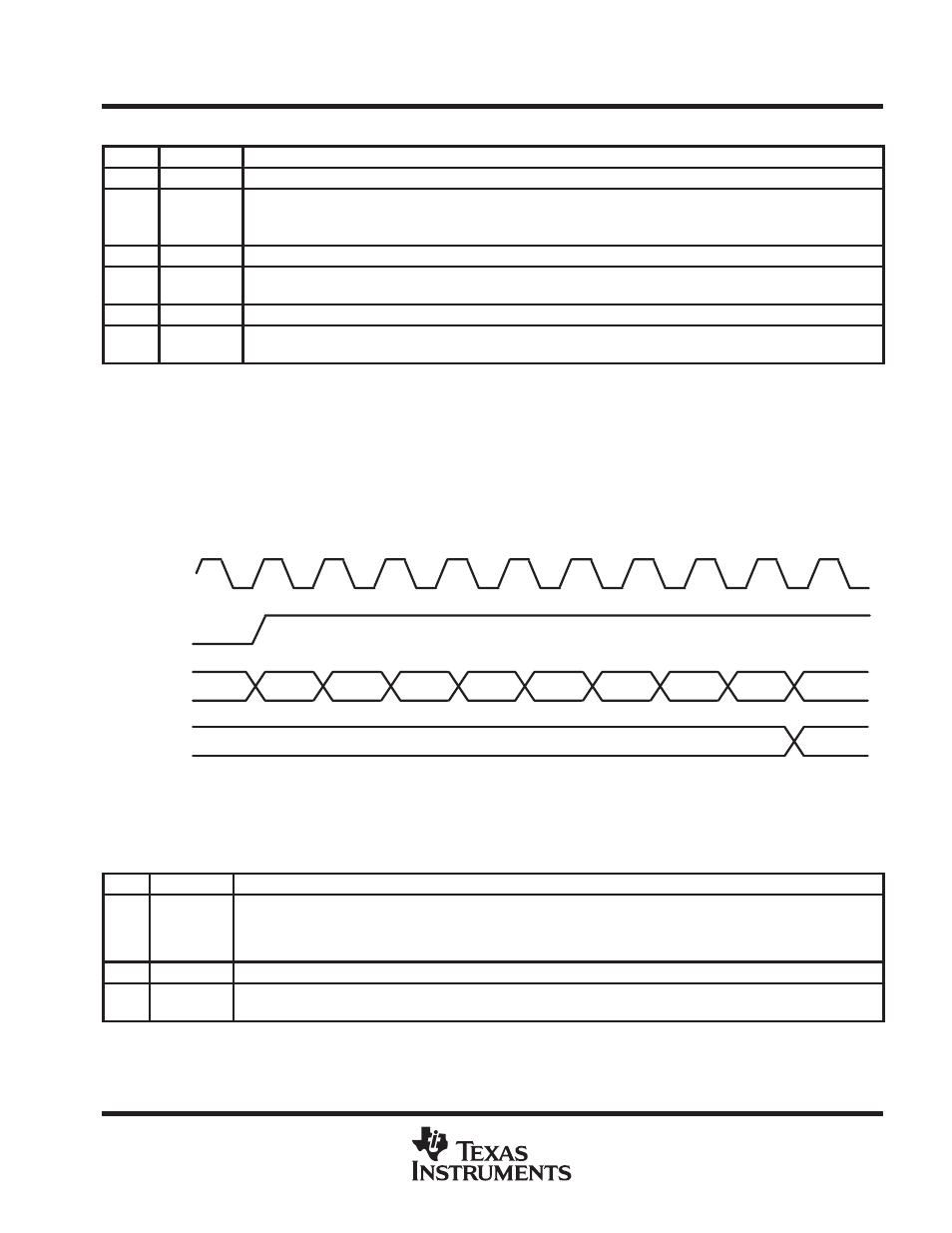

pretag on reception

Port 8 can receive two tag formats, learning and directed, over eight cycles, beginning with the first cycle that

M08_RXDV is high. The pretag takes the form of a 32-bit value (divided into eight nibbles), with each nibble

being replicated on M08_RXD3–M08_RXD0 and M08_RXD7–M08_RXD4. This replaces the preamble and sof

delimiter normally received at this time.

Figure 6 shows the timing relationship, and Table 11 and Table 12 show the fields within the tag for learning and

directed format, respectively.

ООООООООООООООООООООООО

ООООООООООООООООООООООО

ОООО

ОООО

Frame Data

M08_RXD7–

M08_RXD4

ООО

ООО

3–0

7–4

11–8

15–12

19–16

23–20

27–24

31–28

Frame Data

M08_RXD3–

M08_RXD0

M08_RXDV

M08_RCLK

NOTE: Ranges (e.g., 3–0) indicate which bits of the 32-bit pretag are input in each cycle.

Figure 6. Receive Pretag Timing

Table 11. Learning Format Receive Pretag Bit Definitions

BIT

NAME

FUNCTION

31

0

Zero. Indicates learning format. Frames received with this tag format are routed using the device internal frame-routing

algorithm. When the source address is learned, the crossbar matrix port number, indicated by xportcode, also is

learned, and is used to create the xportvector output as part of the transmit pretag for frames subsequently routed to

this address.

30–5

reserved

Reserved. Bits 30–5 are ignored.

4–0

xportcode‡

Source port code. Portcode indicates which port on the device received the frame. Codes 00000–10000 indicate

ports 0–16, respectively. All other codes are reserved and are not generated.

‡ Binary code that selects a single port on this device or an external crossbar matrix connected to port 8