Tnetx4090 thunderswitch ii, Switch – Texas Instruments THUNDERSWITCH II TNETX4090 User Manual

Page 38

TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

38

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

pretagging and extended port awareness

The TNETX4090 can be incorporated into a hierarchical system, whereby this port is connected to a crossbar

matrix with up to 17 1000-Mbit/s ports. By making this TNETX4090 aware of the ports on the crossbar matrix,

the crossbar matrix does not need to make any forwarding or filtering decisions, and can be relatively

inexpensive. To facilitate this, three forms of tags are provided on this port:

D

Pretag on transmission – containing the source port of the frame and a vector indicating the ports on the

crossbar matrix for which the frame is destined.

D

Pretag on reception (learning format) – containing the source port of the frame on the crossbar matrix.

D

Pretag on reception (directed format) – containing a vector indicating the ports on this TNETX4090 for which

the frame is destined.

The information contained within these tags also enables the TNETX4090 to be incorporated in a system where

routing decisions are made at a higher level.

Use of pretagging is enabled by setting pretag in the appropriate PortxControl register.

pretag on transmission

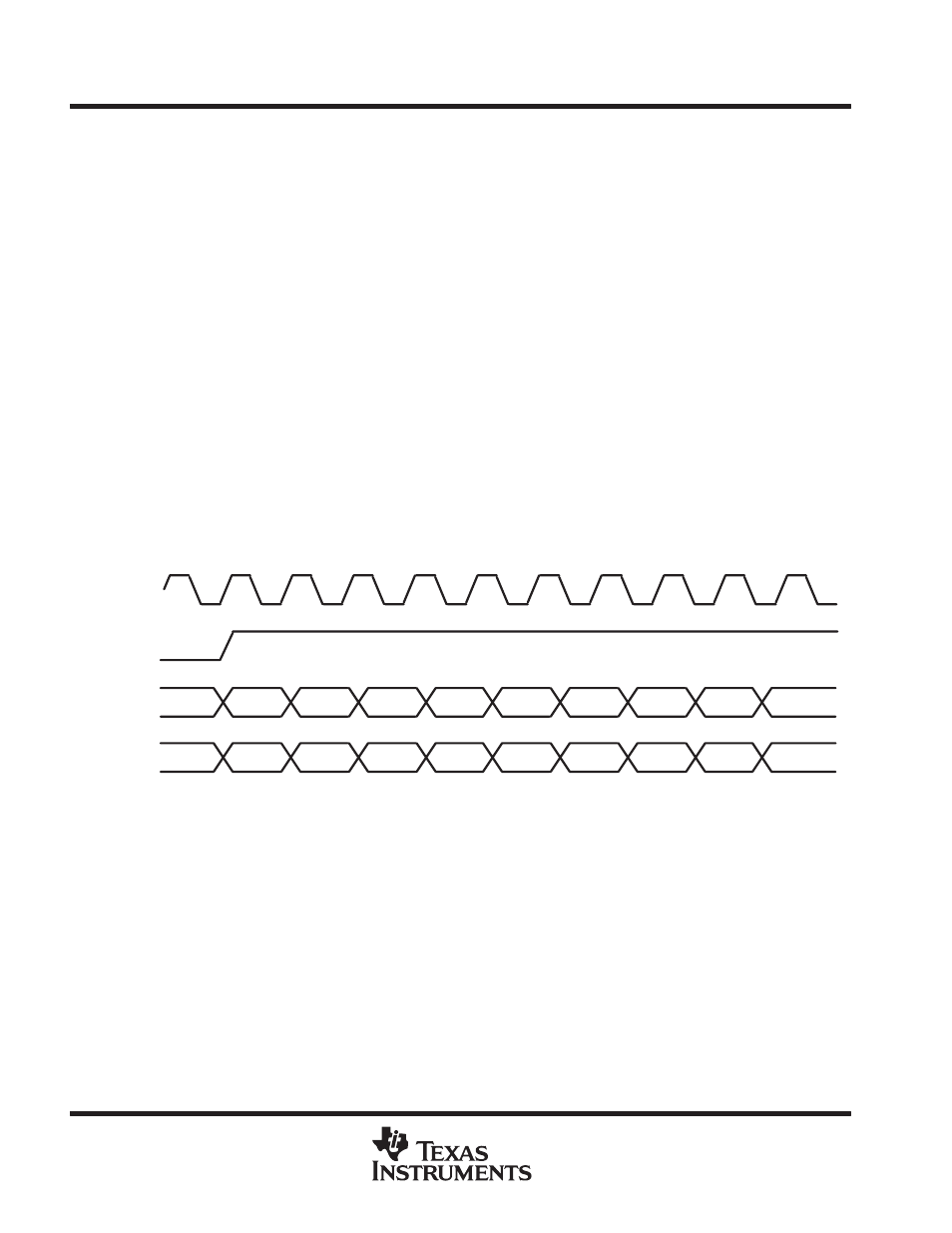

Port 8 provides the frame source port and crossbar matrix destination port vector over eight cycles, beginning

with the first cycle that M08_TXEN is high. The pretag takes the form of a 32-bit value (divided into eight nibbles),

with each nibble being replicated on M08_TXD3–M08_TXD0 and M08_TXD7–M08_TXD4. This replaces the

preamble and sof delimiter normally generated at this time.

Figure 5 shows the timing relationship and Table 10 shows the fields within the tag.

ОООО

ОООО

3–0

7–4

11–8

15–12

19–16

23–20

27–24

31–28

Frame Data

M08_TXD7–

M08_TXD4

ОООО

ОООО

3–0

7–4

11–8

15–12

19–16

23–20

27–24

31–28

Frame Data

M08_TXD3–

M08_TXD0

M08_TXEN

M08_GTCLK

NOTE A: Ranges (e.g., 3–0) indicate which bits of the 32-bit pretag are output in each cycle.

Figure 5. Transmit Pretag Timing