Tnetx4090 thunderswitch ii, Switch – Texas Instruments THUNDERSWITCH II TNETX4090 User Manual

Page 27

TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

27

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

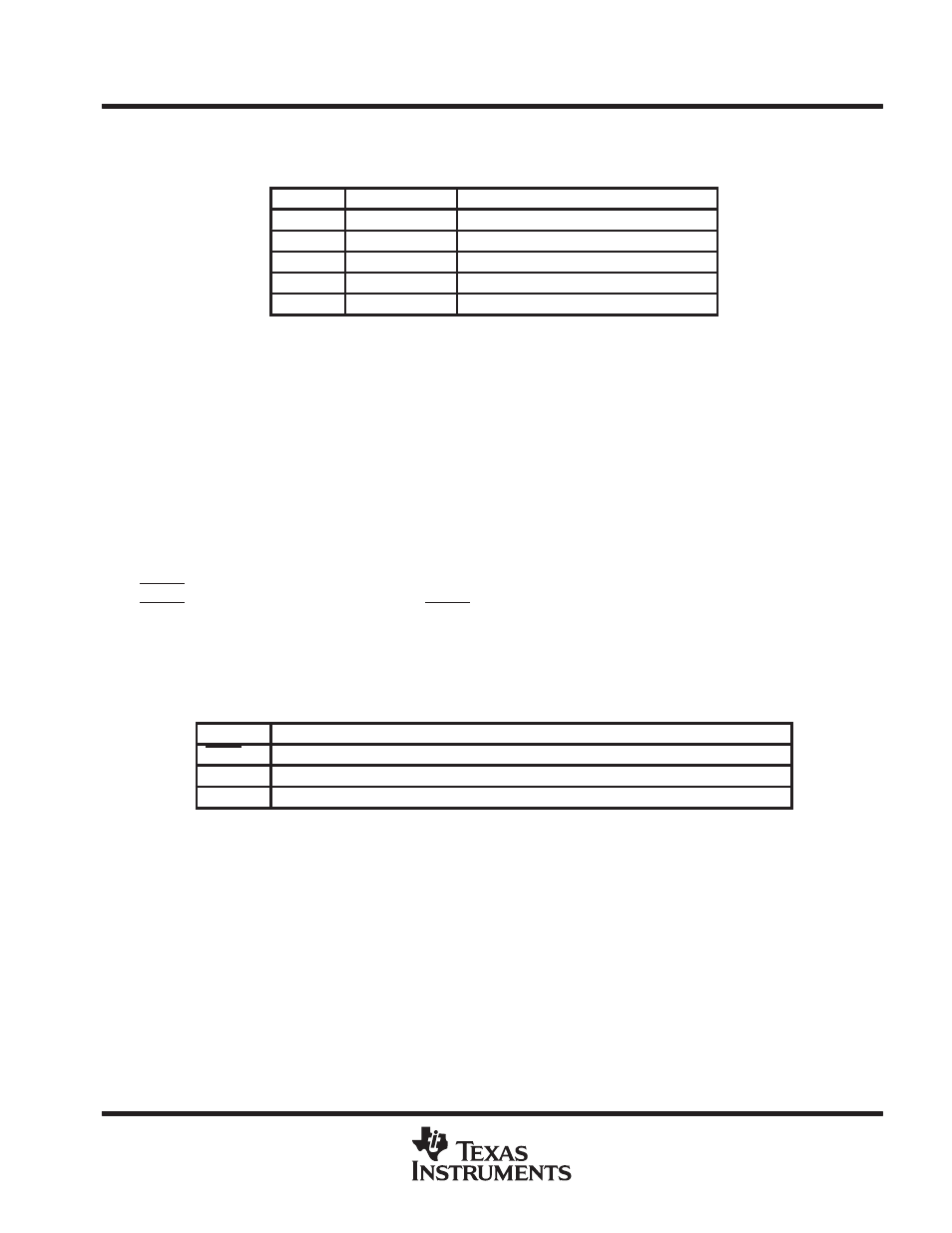

DIO interface description (continued)

Table 5. Address-Lookup Statistics

PORT NO.

HEAD

STATISTIC

N/A

0x9200–0x9FFC

Reserved

N/A

0xA000

Unknown unicast destination addresses

N/A

0xA004

Unknown multicast destination addresses

N/A

0xA008

Unknown source addresses

N/A

0xA00C–0xFFFC

Reserved

When accessing the statistics values from the DIO port, it is necessary to perform four 1-byte DIO reads to obtain

the full 32-bit counter. Counters always should be read in ascending byte-address order (0, 1, 2, 3). To prevent

the counter being updated while reading the four bytes, the entire 32-bit counter value is transferred to a holding

register when byte 0 is read.

To provide ease of use with both big- and little-endian CPUs, two alternative byte-ordering schemes are

supported. The mode of operations can be selected through the StatControl register.

receiving/transmitting management frames

Frames originating within the host are written to the NM port via the NMRxControl and NMData registers. Once

a frame has been fully written, it is then received by the switch and routed to the destination port(s).

Frames that were routed to this port from any of the switch ports are placed in a queue until the host is ready

to read them via the NMTxControl and NMData registers. They then are effectively transmitted out of the switch.

SDMA can be used to transmit or receive management frames (the SAD1–SAD0 terminals are ignored when

SDMA is asserted) (see Table 6). When SDMA is asserted, the switch uses the value in the DMAAddress

register instead of the DIO address registers to access frame data (this also can be used to access the switch

statistics). STXRDY and SRXRDY, the interrupts, freebuffs, eof, sof, and iof mechanisms can be used, as

desired, to prevent unwanted stalls on the DIO bus during busy periods.

Table 6. DMA Interface Signals

SIGNAL

DESCRIPTION

SDMA

Automatically sets up DIO address using the DMAAddress register

STXRDY

Indicates that at least one data frame buffer can be read by the management CPU

SRXRDY

Indicates that the management CPU can write a frame of any size up to 1535 bytes