Tnetx4090 thunderswitch ii, Switch – Texas Instruments THUNDERSWITCH II TNETX4090 User Manual

Page 44

TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

44

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

compatibility with future device revisions

All EEPROM locations that correspond to reserved addresses in the memory map, register bits that are read

only, and register bits that are marked as reserved should be set to 0 to ensure compatibility with future versions

of the device. Failure to do so may result in the unintentional activation of features in future devices. All such

bits are included in the CRC calculation.

LED interface

This interface allows a visual status for each port to be displayed. In addition, the state of the internal flow control

and fault functions are displayed along with 12 software-controllable LEDs.

Each port has a single LED that can convey three states, as shown in Table 15.

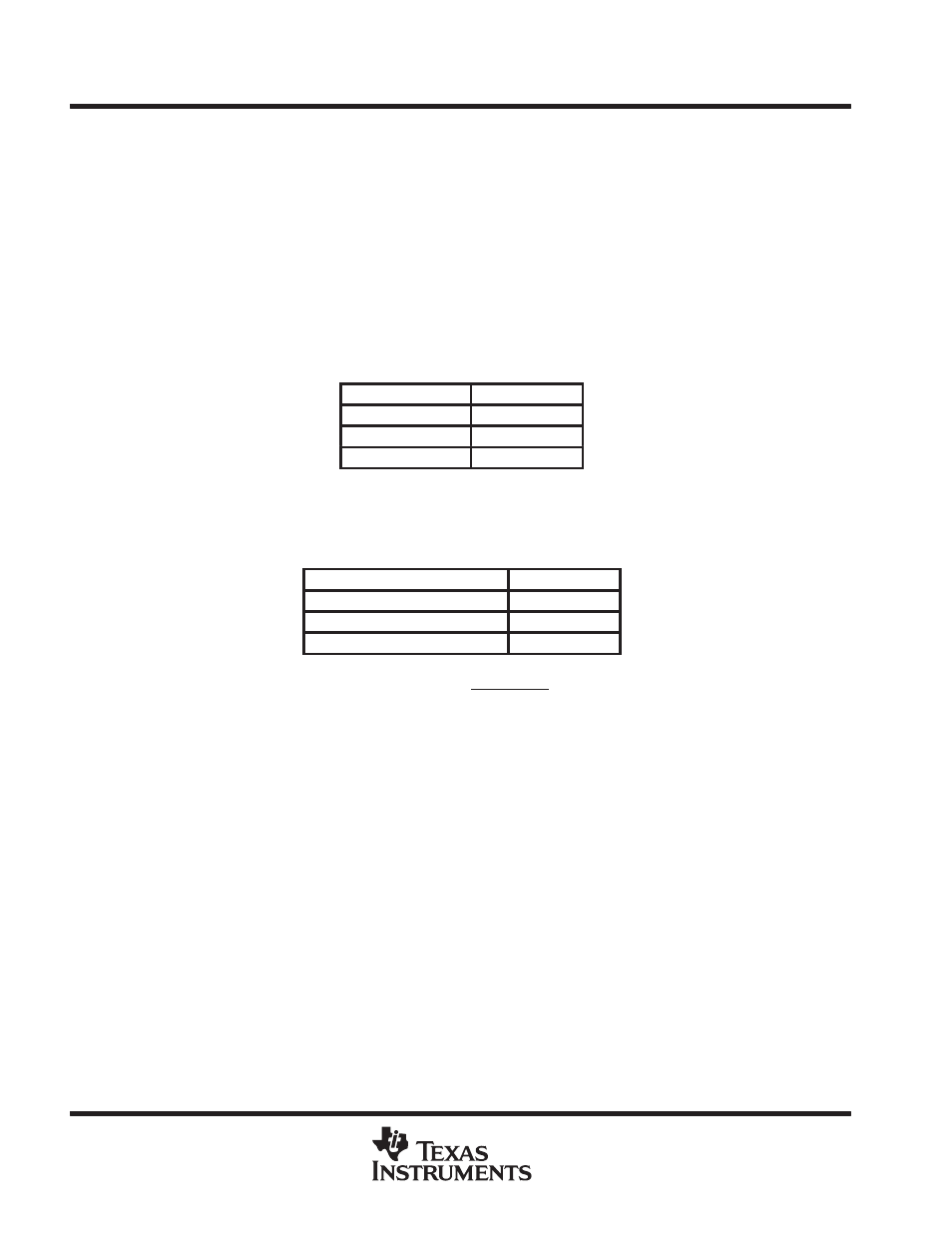

Table 15. Port LED States

STATE

DISPLAY

No link

Off

Link, but no activity

On

Activity

Flashing at 8 Hz

Port 08 has an additional LED, C08, to indicate the occurrence of a collision when operating in PMA mode; this

LED also has three states, as shown in Table 16.

Table 16. Collision LED States

STATE

DISPLAY

No collision (or non PMA mode)

Off

Occasional collision

On

Frequent collisions

Flashing at 8 Hz

The interface is intended for use in conjunction with external octal shift registers, clocked with LED_CLK. Every

1/16th of a second, the status bits are shifted out via LED_DATA.

The status bits are shifted out in one of two possible orders, as determined by slast in LEDControl, to ensure

that systems that do not require all the LED status can be implemented with the minimum number of octal shift

registers.

D

If slast = 0, the software-controlled status bits are shifted out before the port status bits.

D

If slast = 1, the software-controlled status bits are shifted out after the port status bits.

The fault status bit is shifted out last, enabling a minimal system that displays only the fault status to be

implemented without any shift registers.