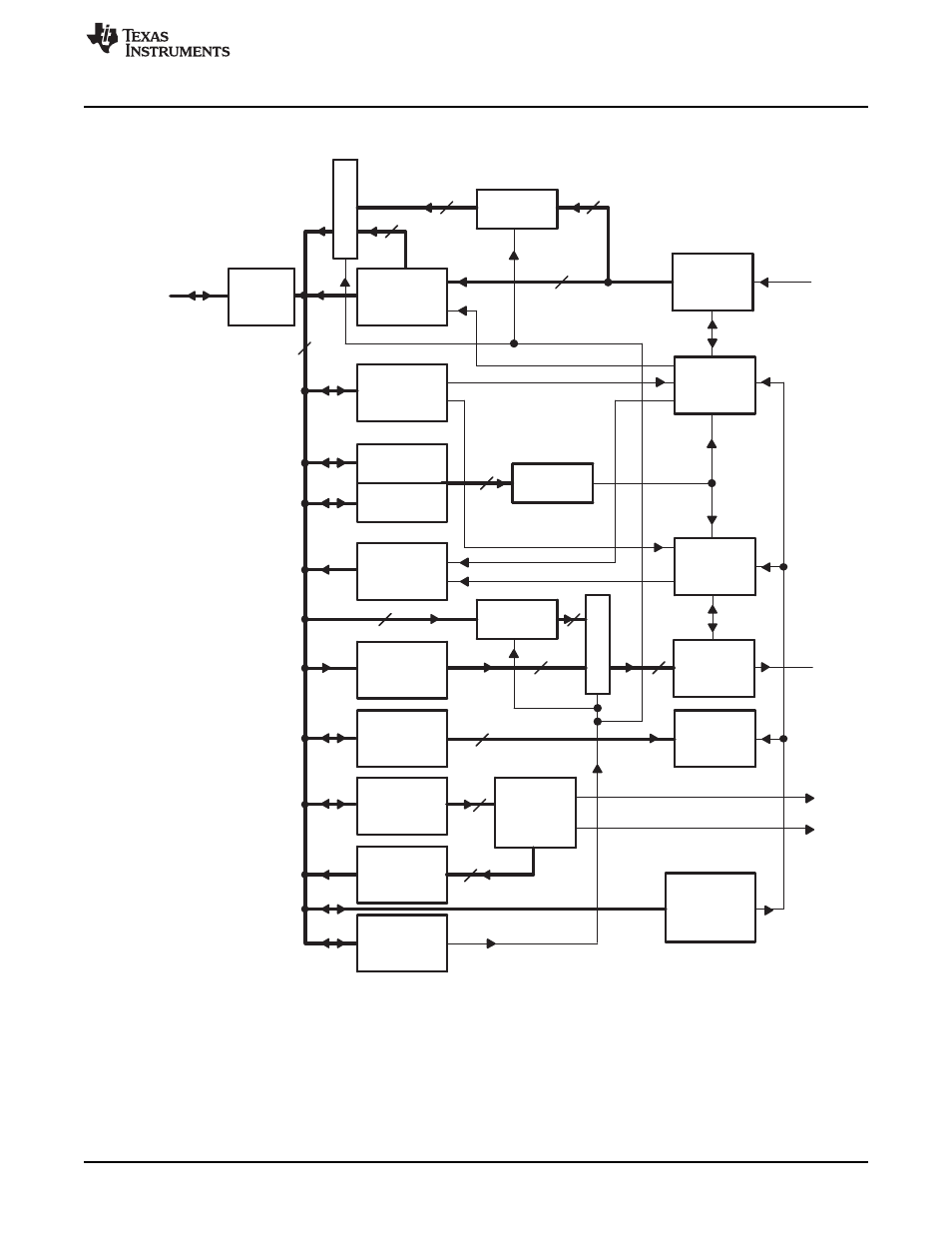

Figure 1 – Texas Instruments TMS320DM643X DMP User Manual

Page 9

8

Receiver

Buffer

Register

Divisor

Latch (LS)

Divisor

Latch (MS)

Baud

Generator

Receiver

FIFO

Line

Status

Register

Transmitter

Holding

Register

Modem

Control

Register

Line

Control

Register

Transmitter

FIFO

Interrupt

Enable

Register

Interrupt

Identification

Register

FIFO

Control

Register

Interrupt/

Event

Control

Logic

S

e

l

e

c

t

Data

Bus

Buffer

RX

TX

Peripheral

Bus

S

e

l

e

c

t

Receiver

Shift

Register

Receiver

Timing and

Control

Transmitter

Timing and

Control

Transmitter

Shift

Register

Control

Logic

16

8

8

8

8

8

Interrupt to CPU

16

8

pin

pin

8

8

8

8

Power and

Emulation

Control

Register

Event to DMA controller

www.ti.com

Introduction

Figure 1. UART Block Diagram

9

SPRU997C – December 2009

Universal Asynchronous Receiver/Transmitter (UART)

Copyright © 2009, Texas Instruments Incorporated

See also other documents in the category Texas Instruments Hardware:

- Digital Signal Processor SM320F2812-HT (153 pages)

- MSP430x1xx (440 pages)

- Laser And Motor Drives DRV8811EVM (13 pages)

- TMS320 DSP (88 pages)

- MSP430x11x1 (45 pages)

- TVP5154EVM (55 pages)

- TMS320DM646X DMSOC (64 pages)

- CC2511 (24 pages)

- SN65HVS880 (4 pages)

- TPS650231EVM (14 pages)

- TMS320TCI648x (256 pages)

- TSC2007EVM-PDK (16 pages)

- UCC38500EVM (16 pages)

- TMS320C6000 (62 pages)

- SCAU020 (21 pages)

- TPS40051 (17 pages)

- TNETE2201 (14 pages)

- TMS320C64x DSP (306 pages)

- UCC2891 (21 pages)

- TMS320C3x (757 pages)

- MSP430 (138 pages)

- TMS320C6712D (102 pages)

- MSP430x4xx (512 pages)

- TMS320C6454 (225 pages)

- SPRU938B (48 pages)

- TUSB3210 (22 pages)

- TMS320C6457 (43 pages)

- CC2530ZNP (3 pages)

- TMS320C6455 (50 pages)

- TSB12LV26 (91 pages)

- TMS320C6472 (2 pages)

- VLYNQ Port (49 pages)

- TMS380C26 (92 pages)

- MSP-FET430 (95 pages)

- TMS320TCI6486 (160 pages)

- TPS2330 (22 pages)

- DM648 DSP (47 pages)

- TMS320DM36X (134 pages)

- MSC1211 (35 pages)

- SPRAA56 (29 pages)

- DAC7741EVM (28 pages)

- CDCM7005 (34 pages)

- TMS370 (99 pages)

- Adpater (37 pages)

- TMS320C6452 DSP (46 pages)