Section 3.6, 6 line control register (lcr) – Texas Instruments TMS320DM643X DMP User Manual

Page 28

Registers

www.ti.com

3.6

Line Control Register (LCR)

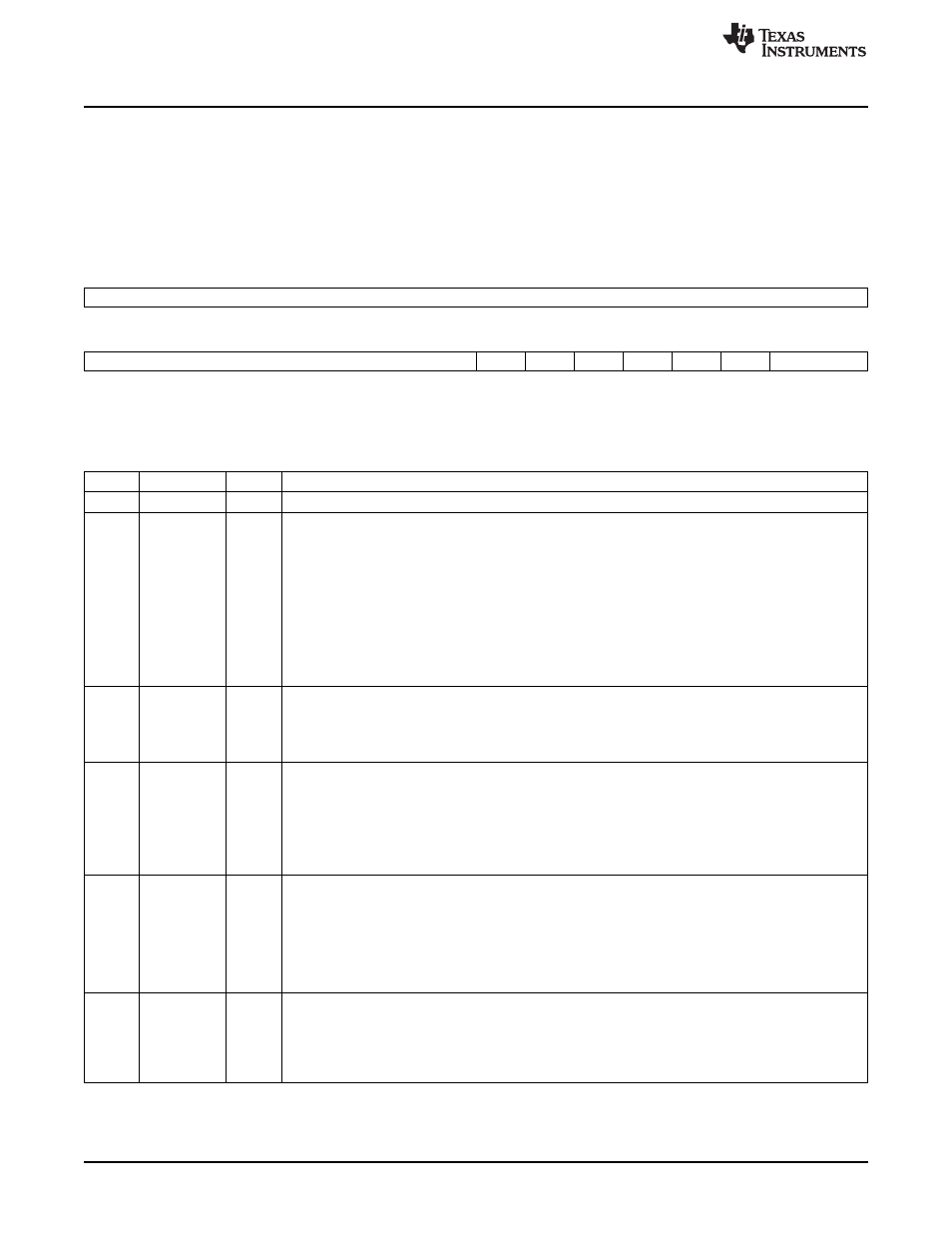

The line control register (LCR) is shown in

and described in

The system programmer controls the format of the asynchronous data communication exchange by using

LCR. In addition, the programmer can retrieve, inspect, and modify the content of LCR; this eliminates the

need for separate storage of the line characteristics in system memory.

Figure 14. Line Control Register (LCR)

31

16

Reserved

R-0

15

8

7

6

5

4

3

2

1

0

Reserved

DLAB

BC

SP

EPS

PEN

STB

WLS

R-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 13. Line Control Register (LCR) Field Descriptions

Bit

Field

Value

Description

31-8

Reserved

0

Reserved

7

DLAB

Divisor latch access bit. The divisor latch registers (DLL and DLH) can be accessed at dedicated

addresses or at addresses shared by RBR, THR, and IER. Using the shared addresses requires

toggling DLAB to change which registers are selected. If you use the dedicated addresses, you can

keep DLAB = 0.

0

Allows access to the receiver buffer register (RBR), the transmitter holding register (THR), and the

interrupt enable register (IER) selected. At the address shared by RBR, THR, and DLL, the CPU can

read from RBR and write to THR. At the address shared by IER and DLH, the CPU can read from and

write to IER.

1

Allows access to the divisor latches of the baud generator during a read or write operation (DLL and

DLH). At the address shared by RBR, THR, and DLL, the CPU can read from and write to DLL. At the

address shared by IER and DLH, the CPU can read from and write to DLH.

6

BC

Break control.

0

Break condition is disabled.

1

Break condition is transmitted to the receiving UART. A break condition is a condition where the

UART_TX signal is forced to the spacing (cleared) state.

5

SP

Stick parity. The SP bit works in conjunction with the EPS and PEN bits. The relationship between the

SP, EPS, and PEN bits is summarized in

0

Stick parity is disabled.

1

Stick parity is enabled.

• When odd parity is selected (EPS = 0), the PARITY bit is transmitted and checked as set.

• When even parity is selected (EPS = 1), the PARITY bit is transmitted and checked as cleared.

4

EPS

Even parity select. Selects the parity when parity is enabled (PEN = 1). The EPS bit works in

conjunction with the SP and PEN bits. The relationship between the SP, EPS, and PEN bits is

summarized in

0

Odd parity is selected (an odd number of logic 1s is transmitted or checked in the data and PARITY

bits).

1

Even parity is selected (an even number of logic 1s is transmitted or checked in the data and PARITY

bits).

3

PEN

Parity enable. The PEN bit works in conjunction with the SP and EPS bits. The relationship between the

SP, EPS, and PEN bits is summarized in

0

No PARITY bit is transmitted or checked.

1

Parity bit is generated in transmitted data and is checked in received data between the last data word

bit and the first STOP bit.

28

Universal Asynchronous Receiver/Transmitter (UART)

SPRU997C – December 2009

Copyright © 2009, Texas Instruments Incorporated