Section 3.7 – Texas Instruments TMS320C674X User Manual

Page 63

www.ti.com

EMAC Control Module Registers

3.7

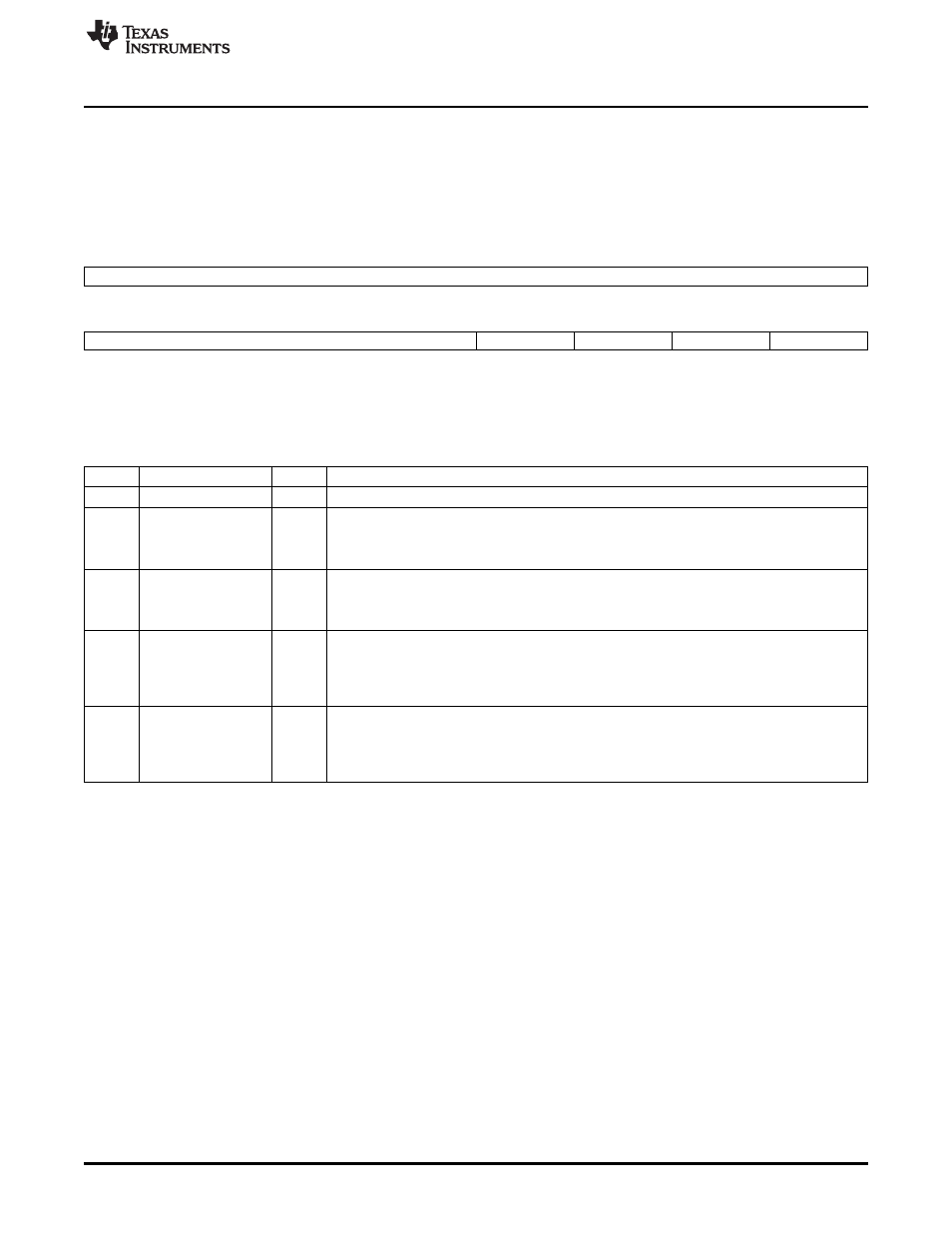

EMAC Control Module Interrupt Core Miscellaneous Interrupt Enable Registers

(C0MISCEN-C2MISCEN)

The EMAC control module interrupt core 0-2 miscellaneous interrupt enable register (CnMISCEN) is

shown in

and described in

Figure 18. EMAC Control Module Interrupt Core 0-2 Miscellaneous Interrupt Enable Register

(CnMISCEN)

31

16

Reserved

R-0

15

4

3

2

1

0

Reserved

STATPENDEN

HOSTPENDEN

LINKINT0EN

USERINT0EN

R-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 15. EMAC Control Module Interrupt Core 0-2 Miscellaneous Interrupt Enable Register

(CnMISCEN)

Bit

Field

Value

Description

31-4

Reserved

0

Reserved

3

STATPENDEN

Enable CnMISCPULSE interrupt generation when EMAC statistics interrupts are generated

0

CnMISCPULSE generation is disabled for EMAC STATPEND interrupts.

1

CnMISCPULSE generation is enabled for EMAC STATPEND interrupts.

2

HOSTPENDEN

Enable CnMISCPULSE interrupt generation when EMAC host interrupts are generated

0

CnMISCPULSE generation is disabled for EMAC HOSTPEND interrupts.

1

CnMISCPULSE generation is enabled for EMAC HOSTPEND interrupts.

1

LINKINT0EN

Enable CnMISCPULSE interrupt generation when MDIO LINKINT0 interrupts (corresponding to

USERPHYSEL0) are generated

0

CnMISCPULSE generation is disabled for MDIO LINKINT0 interrupts.

1

CnMISCPULSE generation is enabled for MDIO LINKINT0 interrupts.

0

USERINT0EN

Enable CnMISCPULSE interrupt generation when MDIO USERINT0 interrupts (corresponding

to USERACCESS0) are generated

0

CnMISCPULSE generation is disabled for MDIO USERINT0.

1

CnMISCPULSE generation is enabled for MDIO USERINT0.

63

SPRUFL5B – April 2011

EMAC/MDIO Module

© 2011, Texas Instruments Incorporated