Section 5.35, Section 5.36 – Texas Instruments TMS320C674X User Manual

Page 116

EMAC Module Registers

www.ti.com

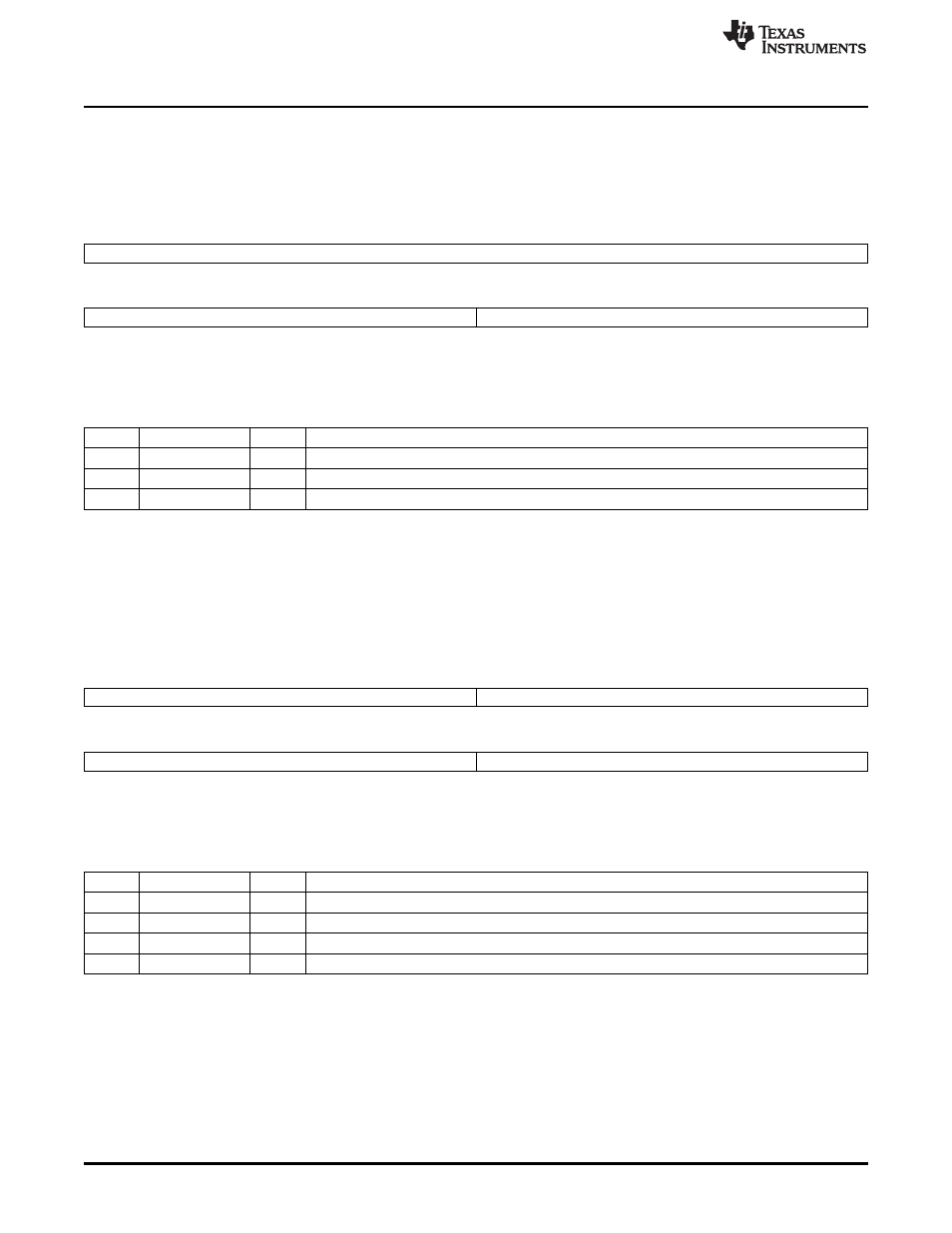

5.35 MAC Source Address Low Bytes Register (MACSRCADDRLO)

The MAC source address low bytes register (MACSRCADDRLO) is shown in

and described in

Figure 73. MAC Source Address Low Bytes Register (MACSRCADDRLO)

31

16

Reserved

R-0

15

8

7

0

MACSRCADDR0

MACSRCADDR1

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 72. MAC Source Address Low Bytes Register (MACSRCADDRLO) Field Descriptions

Bit

Field

Value

Description

31-16

Reserved

0

Reserved

15-8

MACSRCADDR0

0-FFh

MAC source address lower 8-0 bits (byte 0)

7-0

MACSRCADDR1

0-FFh

MAC source address bits 15-8 (byte 1)

5.36 MAC Source Address High Bytes Register (MACSRCADDRHI)

The MAC source address high bytes register (MACSRCADDRHI) is shown in

and described in

Figure 74. MAC Source Address High Bytes Register (MACSRCADDRHI)

31

24

23

16

MACSRCADDR2

MACSRCADDR3

R/W-0

R/W-0

15

8

7

0

MACSRCADDR4

MACSRCADDR5

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 73. MAC Source Address High Bytes Register (MACSRCADDRHI) Field Descriptions

Bit

Field

Value

Description

31-24

MACSRCADDR2

0-FFh

MAC source address bits 23-16 (byte 2)

23-16

MACSRCADDR3

0-FFh

MAC source address bits 31-24 (byte 3)

15-8

MACSRCADDR4

0-FFh

MAC source address bits 39-32 (byte 4)

7-0

MACSRCADDR5

0-FFh

MAC source address bits 47-40 (byte 5)

116

EMAC/MDIO Module

SPRUFL5B – April 2011

© 2011, Texas Instruments Incorporated