Texas Instruments TMS320C674X User Manual

Page 113

www.ti.com

EMAC Module Registers

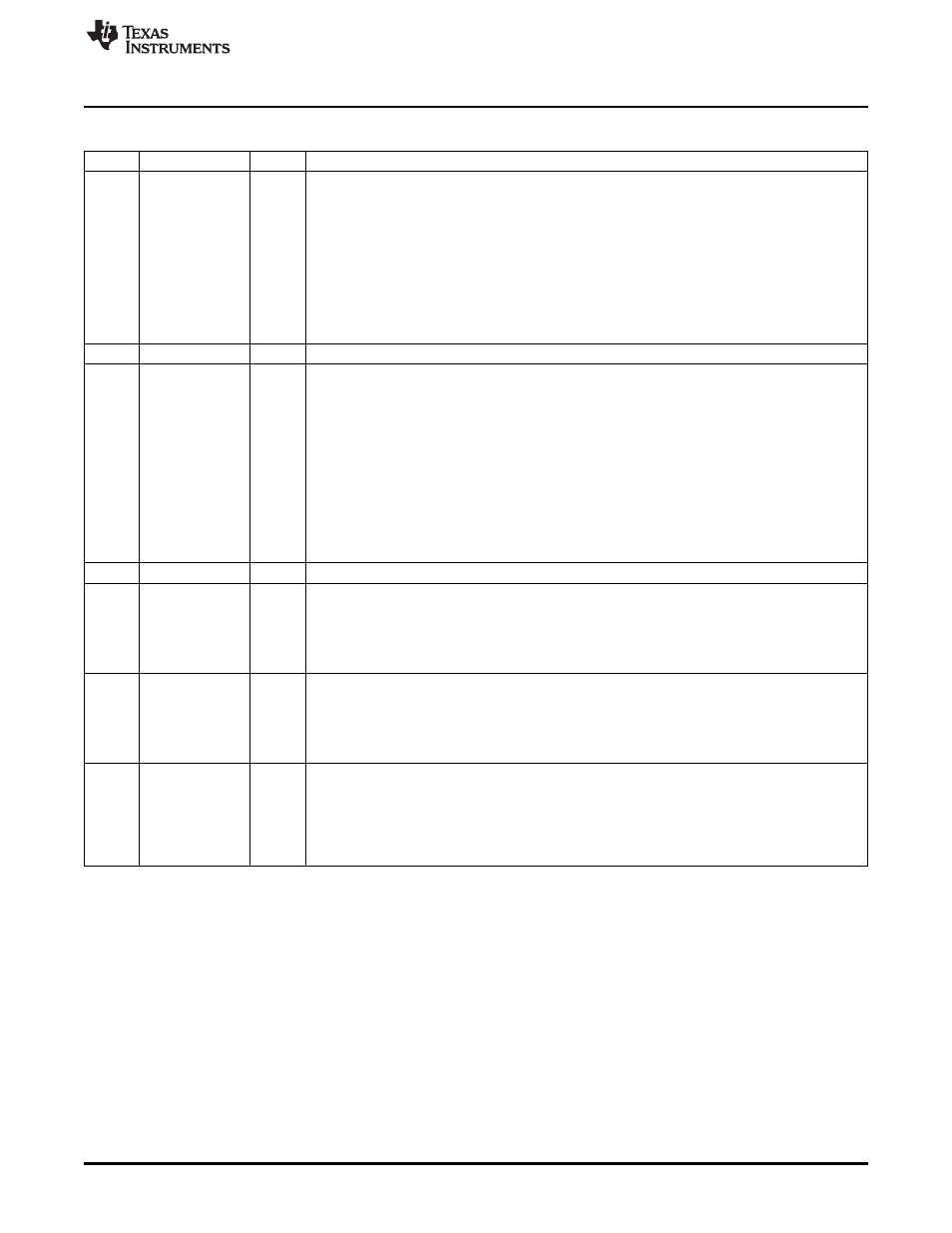

Table 67. MAC Status Register (MACSTATUS) Field Descriptions (continued)

Bit

Field

Value

Description

15-12

RXERRCODE

0-Fh

Receive host error code. These bits indicate that EMAC detected receive DMA related host errors.

The host should read this field after a host error interrupt (HOSTPEND) to determine the error. Host

error interrupts require hardware reset in order to recover.

0

No error

1h

Reserved

2h

Ownership bit not set in SOP buffer

3h

Reserved

4h

Zero buffer pointer

5h-Fh

Reserved

11

Reserved

0

Reserved

10-8

RXERRCH

0-7h

Receive host error channel. These bits indicate which receive channel the host error occurred on.

This field is cleared to 0 on a host read.

0

The host error occurred on receive channel 0

1h

The host error occurred on receive channel 1

2h

The host error occurred on receive channel 2

3h

The host error occurred on receive channel 3

4h

The host error occurred on receive channel 4

5h

The host error occurred on receive channel 5

6h

The host error occurred on receive channel 6

7h

The host error occurred on receive channel 7

7-3

Reserved

0

Reserved

2

RXQOSACT

Receive Quality of Service (QOS) active bit. When asserted, indicates that receive quality of service

is enabled and that at least one channel freebuffer count (RXnFREEBUFFER) is less than or equal

to the RXFILTERLOWTHRESH value.

0

Receive quality of service is disabled.

1

Receive quality of service is enabled.

1

RXFLOWACT

Receive flow control active bit. When asserted, at least one channel freebuffer count

(RXnFREEBUFFER) is less than or equal to the channel's corresponding RXnFILTERTHRESH

value.

0

Receive flow control is inactive.

1

Receive flow control is active.

0

TXFLOWACT

Transmit flow control active bit. When asserted, this bit indicates that the pause time period is being

observed for a received pause frame. No new transmissions will begin while this bit is asserted,

except for the transmission of pause frames. Any transmission in progress when this bit is asserted

will complete.

0

Transmit flow control is inactive.

1

Transmit flow control is active.

113

SPRUFL5B – April 2011

EMAC/MDIO Module

© 2011, Texas Instruments Incorporated