NEC PD75P308 User Manual

Page 21

µ

PD75P308

21

1600

ns

t

KCY

/2

-50

150

ns

t

KCY

/2

ns

0

250

ns

t

KCY

ns

t

KCY

ns

t

KCY

ns

t

KCY

ns

SCK Cycle Time

SCK High-, Low-Level

Widths

SB0, 1 Set-Up Time (vs. SCK )

SB0, 1 Hold Time (vs. SCK )

SCK SB0, 1 Output

Delay Time

SCK SB0, 1

SB0, 1 SCK

SB0, 1 Low-Level Width

SB0, 1 High-Level Width

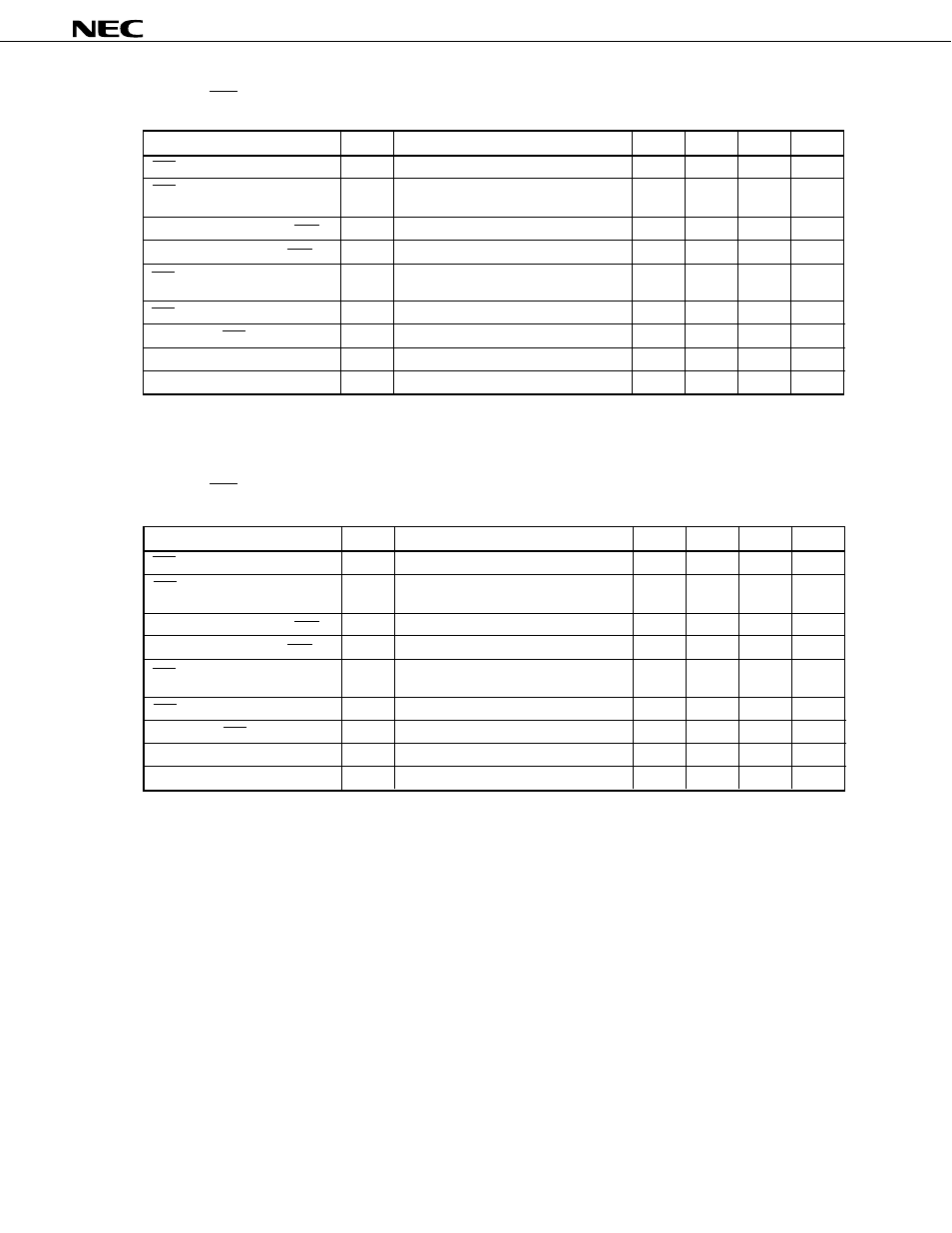

SBI MODE (SCK: internal clock output (master))

Parameter

Symbol

Conditions

MIN.

TYP.

MAX.

Unit

t

KCY3

t

KL3

t

KH3

t

SIK3

t

KSI3

t

KSO3

t

KSB

t

SBK

t

SBL

t

SBH

*: R

L

and C

L

are load resistance and load capacitance of the SO output line.

SBI MODE (SCK: external clock output (master))

*: R

L

and C

L

are load resistance and load capacitance of the SO output line.

↑

↑

R

L

= 1k

Ω

, C

L

=

100pF*

↓ →

↑ →

↓

↓ →

↓

SCK Cycle Time

SCK High-, Low-Level

Widths

SB0, 1 Set-Up Time (vs. SCK )

SB0, 1 Hold Time (vs. SCK )

SCK SB0, 1 Output

Delay Time

SCK SB0, 1

SB0, 1 SCK

SB0, 1 Low-Level Width

SB0, 1 High-Level Width

Parameter

Symbol

Conditions

MIN.

TYP.

MAX.

Unit

1600

ns

100

ns

t

KCY

/2

ns

0

300

ns

t

KCY

ns

t

KCY

ns

t

KCY

ns

t

KCY

ns

t

KCY4

t

KL4

t

KH4

t

SIK4

t

KSI4

t

KSO4

t

KSB

t

SBK

t

SBL

t

SBH

↑

↑

R

L

= 1k

Ω

, C

L

=

100pF*

↓ →

↑ →

↓

↓ →

↓

★

★

ns

400

ns