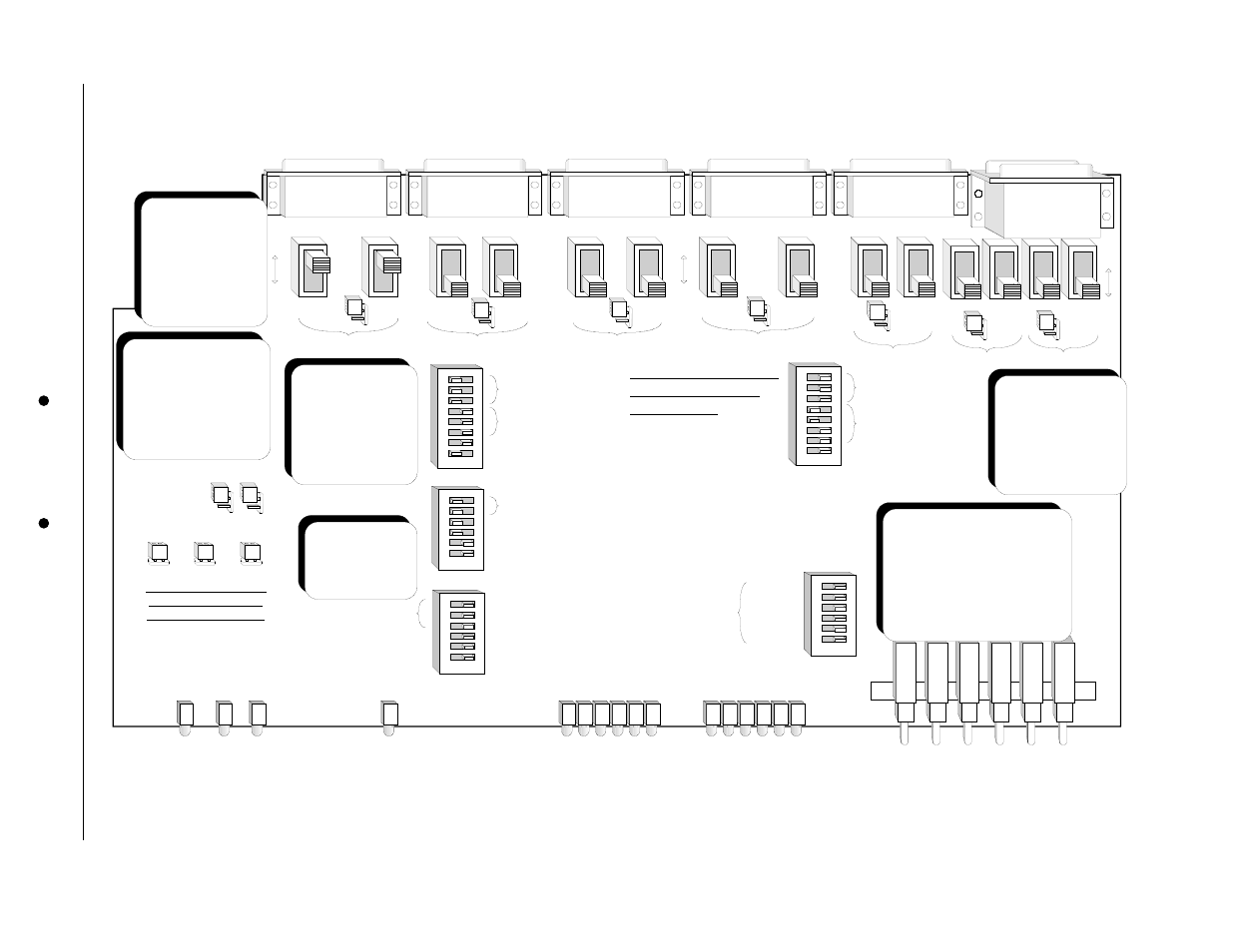

Port enabled = green, Master port 3 port 4 port 5 port 6, Port 2 port 1 – Patton electronic 3060/V24 User Manual

Page 21: Master port 1 port 2 port 3 port 4, Port 1, Clock fall back, Port 5, Port 6, Dce d t e

3060/V24

102001UA

A-5

A

PPENDIX

P

ATTON

E

LECTRONICS

C

O

.I

NSTALLATION

A

ND

O

PERATIONS

M

ANUAL

Port Enabled = GREEN

S W 7

S W 10

S W 9

S W 1 4

S W 13

S W 1 6

S W 1 5

S W 17

S W 18

S W 2 0

S W 12

S W 19

S W 1 1

S W 8

Master

Port 1

Port 2

Port 3

Port 4

Master

Port 3

Port 4

Port 5

Port 6

Port 2

Port 3

Port 4

Port 5

Port 6

P W R T X D R X D

Sub-Channel Active

Anti-Stream

Not Used

Port 1

NOTE: Both TX & RX

Clk Source MUST

be Selected

DCE

D

T

E

Clock Fall Back

DCE

D

T

E

DCE

D

T

E

Port 5

S W 2 1

S W 2 3

S W 2 4

S W 2 2

S W 2 5

J P 1 0

J P 9

J P 1 1

J P 1 2

J P 8

J P 7

J P 6

J P 4

J P 5

J P 3

J P 2

J P 1

Not Used

Priority Mode = ON / Scan Mode = OFF

RX Clock Source

6

5

4

3

2

1

6

5

4

3

2

1

Fallback Disable = ON / Enable = OFF

Fallback Source, CLK Trans = ON / Chan 1 DCD = OFF

Data To Channels Gated = ON / Broadcast = OFF

Anti-Stream Enable = ON / Disable = OFF

No Data Time Out Count

Channel 6

Channel 5

Channel 4

Channel 3

Channel 2

Channel 1

Chassis Gnd Connected to Signal Gnd= ON

Anti-Stream Timer Select

Sync = ON / Async = OFF

Internal Baud Rate Selection

C T S D e l a y T i m e

O N

O F F

3

4

5

62

1

O N

O F F

3

4

5

62

1

O N

O F F

3

4

5

62

1

3

4

5

6

7

8

2

1

O N

O F F

TX Clock Source

TXC Source Pin 15 = ON / Pin 24 = OFF

Channel Activity Indicated By

Control = ON / Data = OFF

Port 2

Port 1

Plus Test Voltage

Enable / Disable

Minus Test Voltage

Enable / Disable

Factory Test Jumpers

Must Be INSTALLED

For Unit to OPERATE

3

4

5

6

7

8

2

1

O N

O F F

JP6 Thru JP12 Force DTR (20) / DSR(6) Active on the Master or Associated Port

Anti-Stream Timer SW21

3

O N

O N

O N

O N

O F F

O F F

O F F

O F F

2

O N

O N

O F F

O F F

O N

O N

O F F

O F F

1

O N

O F F

O N

O F F

O N

O F F

O N

O F F

Count

1 0 2 4

2 0 4 8

4 0 9 6

1 6 K

6 4 K

2 5 6 K

1 M e g

2 M e g

TX Clock Source SW21

6

O N

O N

O N

O N

O F F

O F F

O F F

O F F

5

O N

O N

O F F

O F F

O N

O N

O F F

O F F

4

O N

O F F

O N

O F F

O N

O F F

O N

O F F

Source

M a s t e r

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Internal

RX Clock Source SW24

3

O N

O N

O N

O N

O F F

O F F

O F F

O F F

2

O N

O N

O F F

O F F

O N

O N

O F F

O F F

1

O N

O F F

O N

O F F

O N

O F F

O N

O F F

Source

M a s t e r

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Internal

No Data Time Out SW23

1

O N

O N

O F F

O F F

2

O N

O F F

O N

O F F

T O Count

1 6

6 4

2 5 6

2 0 4 8

Internal Baud Rate SW22

6

O N

O N

O N

O N

O F F

O F F

O F F

O F F

5

O N

O N

O F F

O F F

O N

O N

O F F

O F F

4

O N

O F F

O N

O F F

O N

O F F

O N

O F F

C h a n 6 R X C

7 6 8 0 0

3 8 4 0 0

1 9 2 0 0

9 6 0 0

4 8 0 0

2 4 0 0

1 2 0 0

Pos 7=ON

5 7 6 0 0

2 8 8 0 0

1 4 4 0 0

7 2 0 0

3 6 0 0

1 8 0 0

9 0 0

Pos 7=OFF

CTS Delay SW22

3

O N

O N

O N

O N

O F F

O F F

O F F

O F F

2

O N

O N

O F F

O F F

O N

O N

O F F

O F F

Delay

No Delay

1 m S

2 m S

4 m S

9 m S

1 8 m S

3 6 m S

7 2 m S

1

O N

O F F

O N

O F F

O N

O F F

O N

O F F

Port 6