PC Concepts SHG2 DP User Manual

Page 27

Intel® SHG2 DP Server Board Technical Product Specification

Processor and Chipset

Revision 1.0

Intel Order Number C11343-001

15

2.5.1.2 Parallel

Port

The SHG2 baseboard provides a 25-pin parallel port connector.

The SIO provides an IEEE

1284-compliant, 25-pin bi-directional parallel port.

BIOS programming of the SIO registers

enables the parallel port and determines the port address and interrupt.

When disabled, the

interrupt is available to add in adapters. Parallel port pinouts are shown in Table 4.

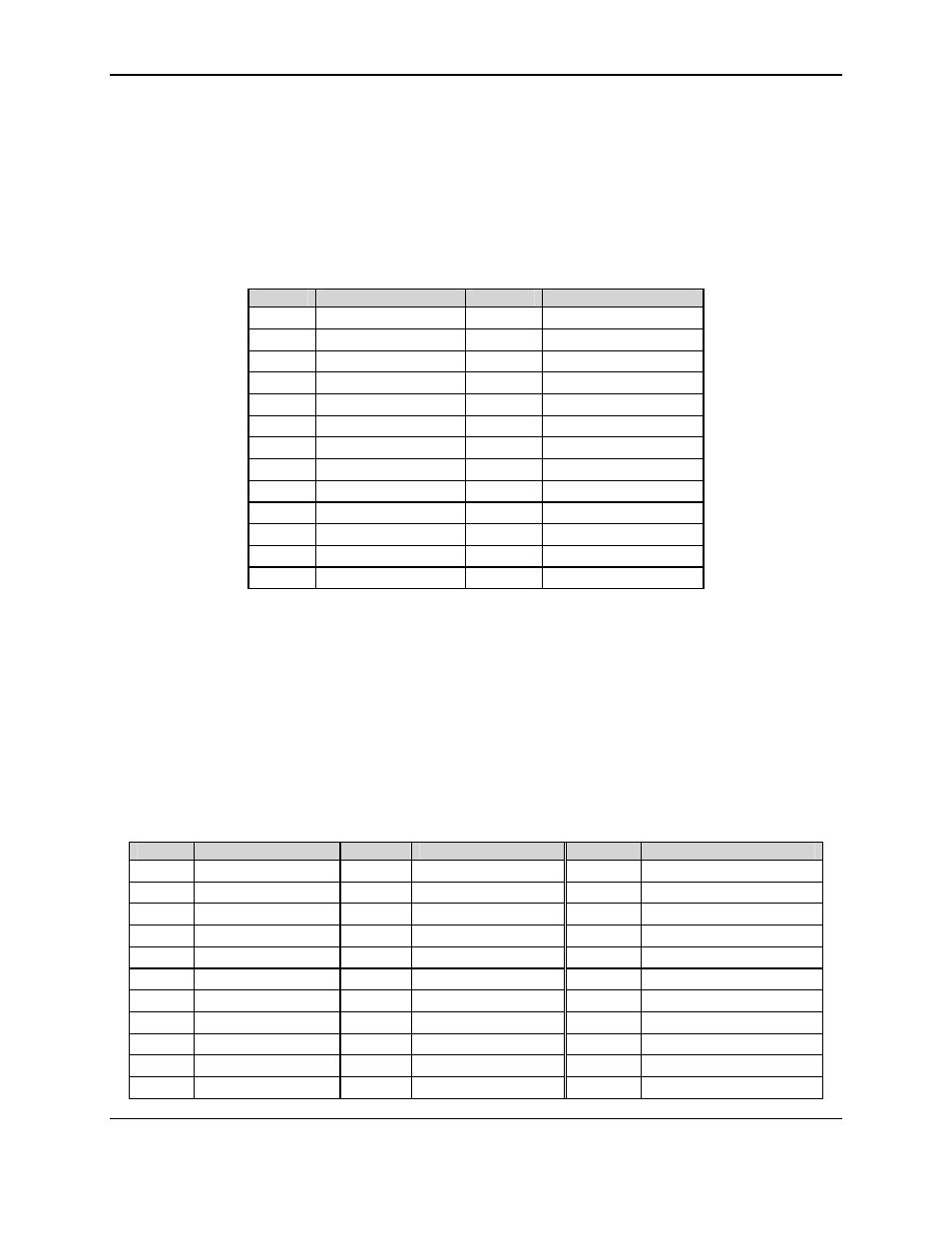

Table 4. Parallel Port Connector Pinout

Pin

Name

Pin

Name

1 STROBE_L

14 AUFDXT_L

2 D0

15 ERROR_L

3 D1

16 INIT_L

4 D2

17 SLCTIN_L

5 D3

18 GND

6 D4

19 GND

7 D5

20 GND

8 D6

21 GND

9 D7

22 GND

10 ACK_L

23 GND

11 BUSY

24 GND

12 PE

25 GND

13 SLCT

2.5.1.3 Floppy

Port

The Floppy Disk Controller (FDC) is located in the the Super I/O controller (SIO). The SIO is

software compatible with the PC8477, which contains a superset of the FDC functions in the

uDP8473, NEC uPD765A, and N82077. The baseboard provides the 48-MHz clock,

termination resistors, and chip selects.

All other FDC functions are integrated into the SIO,

including analog data separator and 16-byte FIFO. The FDC connector pinouts are shown

below in Table 5.

Table 5. Floppy Port Connector Pinout

Pin

Name

Pin

Name

Pin

Name

1 GND

13 GND

25 GND

2 FD_DENSEL 14 FD_DR0_L

26 FD_TRK0_L

3 GND

15 GND

27 FD_MSEN0

4 N/C

16 FD_MTR1_L

28 FD_WPROT_L

5 Key

17 FD_MSEN1

29 GND

6 FD_DRATE0 18 FD_DIR_L

30 FD_RDATA_L

7 GND

19 GND

31 GND

8 FD_INDEX_L 20 FD_STEP_L

32 FD_HDSEL_L

9 GND

21 GND

33 GND

10 FD_MTR0_L

22 FD_WDATA_L 34 FD_DSKCHG_L

11 GND

23 GND