Status register, Table 3-14. status register – Lantronix DSTni-EX User Manual

Page 34

26

Bits

Field Name

Description

2

AAK

Acknowledge

1 = send Acknowledge (LOW level on SDA) during acknowledge clock pulse on

the I

2

C bus if:

−The entire 7-bit slave address or the first or second bytes of a 10-bit slave

address are received.

− The general call address is received and the GCE bit in the ADDR register is

set to one.

− A data byte is received in master or slave mode.

0 in slave transmitter mode = send Not Acknowledge (HIGH level on SDA) when

a data byte is received in master or slave mode. After this byte transmits, the I

2

C

controller enters state C8h and returns to idle state. The I

2

C controller does not

respond as a slave unless AAK is set.

1:0

///

Reserved

Status Register

The Status register is a Read Only register that contains a 5-bit status code in the five most-

significant bits. The three least-significant bits are always zero. This register can contain any of

the 31 status codes in Table 3-16. When this register contains the status code F8h:

No relevant status information is available.

No interrupt is generated.

The IFLG bit in the Control register is not set.

All other status codes correspond to a defined state of the I

2

C controller, as described in Table

When entering each of these states, the corresponding status code appears in this register and

the IFLG bit in the Control register is set. When the IFLG bit clears, the status code returns to

F8h

If an illegal condition occurs on the I

2

C bus, the bus enters the bus error state (status code 00h).

To recover from this state, set the STP bit in the Control register and clear the IFLG bit. The I

2

C

controller then returns to the idle state. No STOP condition transmits on the I

2

C bus.

Note:

The STP and STA bits can be set to 1 at the same time to recover from the bus error,

causing the I

2

C controller to send a START.

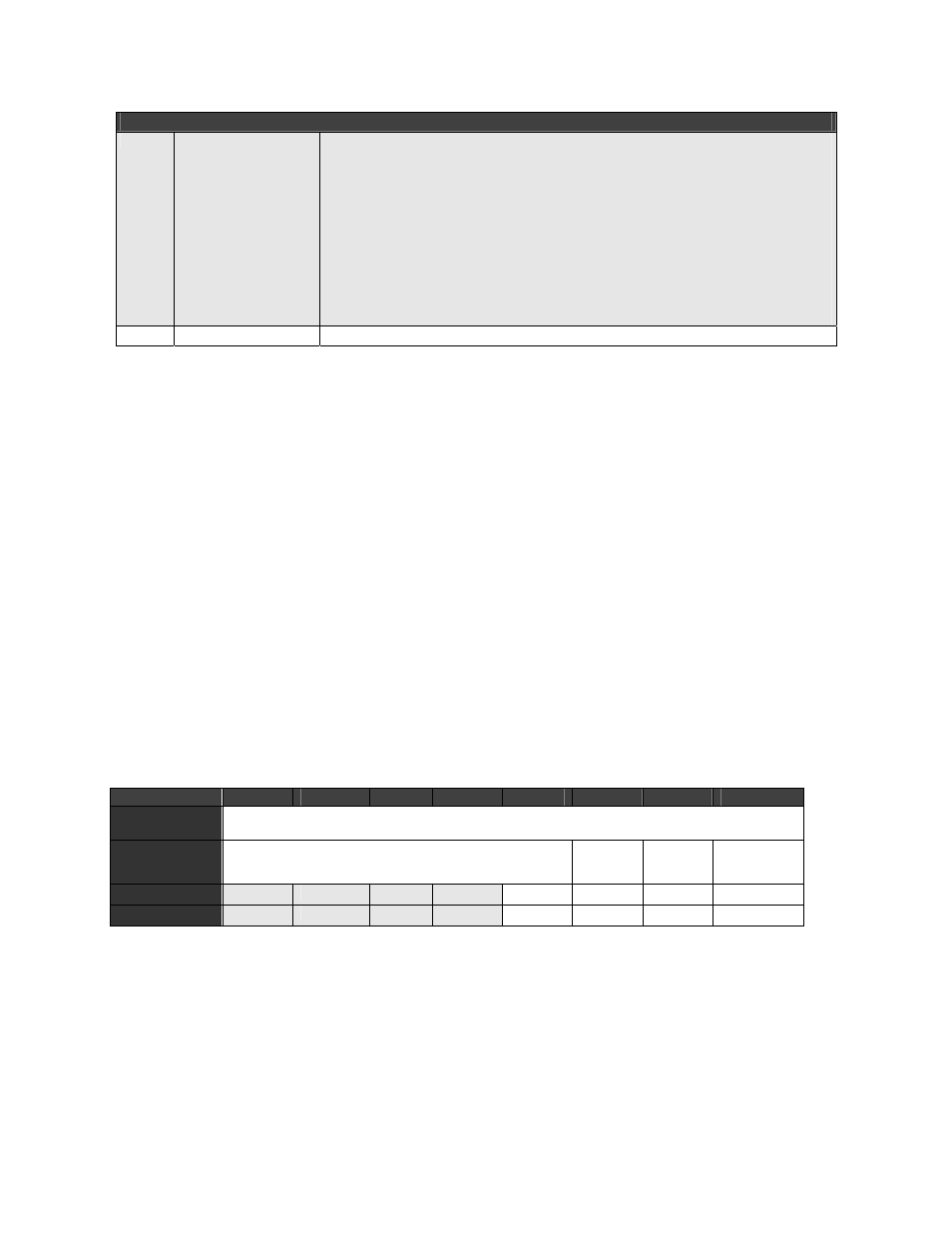

Table 3-14. Status Register

BIT

7

6

5

4

3

2

1

0

OFFSET

D006

FIELD

STATUS CODE

///

///

///

RESET

0

0

0

0

0 0 0 0

RW

R

R

R

R

R R R R