SMC Networks SMC91C95 User Manual

Page 82

82

PCMCIA CONFIGURATION REGISTERS DESCRIPTION

Ethernet Function (Base Address 8000h)

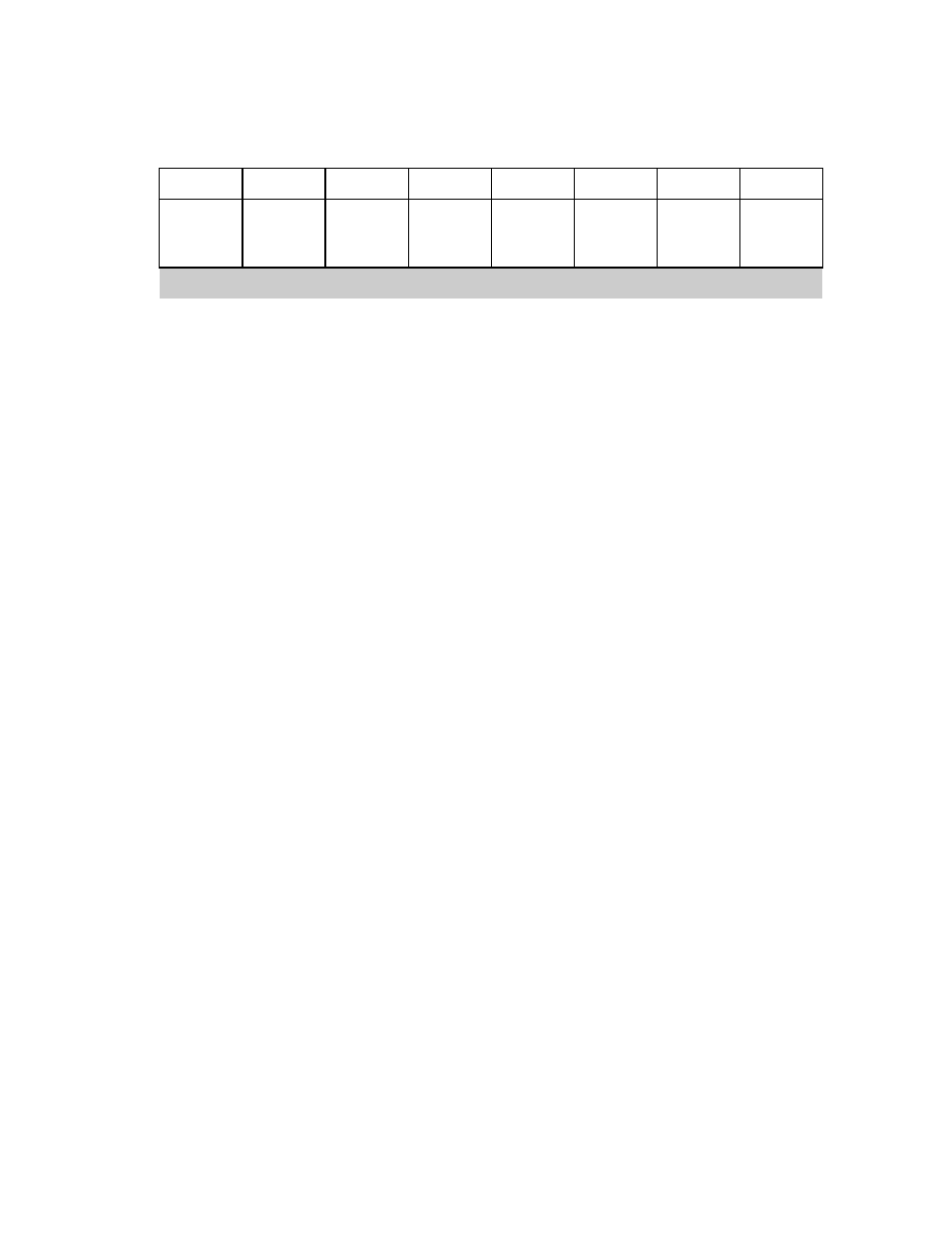

8000h - Ethernet Configuration Option Register (ECOR)

7

6

5

4

3

2

1

0

SRESET

LevIREQ

WRATTRI

B

Enable

IREQ

Enable

Base and

Limit

Enable

Function

0

1

0

0

0

0

0

0

BIT 7 - SRESET: This bit when set will clear all

internal registers associated with the Ethernet

function except itself.

BIT 6 - LevIREQ: This bit is read only and reads

as a one to indicate level mode interrupts are

used. Pulse mode interrupts are not supported.

BIT 5 - Not defined

BIT 4 - Not defined

BIT 3 - WRATTRIB: This bit when when set (1),

allows writting into the external attribute

memory space.

BIT 2 - Enable IREQ Routing: This bit enables

(1) or disables (0) the Ethernet function from

asserting nIREQ. The nIREQ pin on power up

and RESET is in a high (1) de-asserted state.

BIT 1 - Enable Base and Limit: This bit enables

the on board I/O base decoder. If set, the on-

board decoder is used to select the function. If

cleared, the decoder is disabled and it is

assumed that the host provides for the

decoding. When the decode is disabled, the

function is enabled, and is configured for 16 bits

(and not in power-down mode), the signal -

IOIs16 is always asserted. It is then up to the

host to qualify the usage of -IOIs16. For

multifunction PCMCIA functionality, this

bit must be set.

BIT 0 - Enable Function: This bit enables (1) or

disables (0) the Ethernet function. While the

Ethernet function is disabled it remains in

powerdown mode, no access to the Ethernet

I/O space (ie. The bank register are not

accessable) is allowed. IREQ is not generated

for this function and nINPACK is not returned

for accesses to the Ethernet registers.

If the “Magic Packet” function is enabled, the

device is not completly powered down. The

MAC controller is still enabled to receive.