SMC Networks SMC91C95 User Manual

Page 50

50

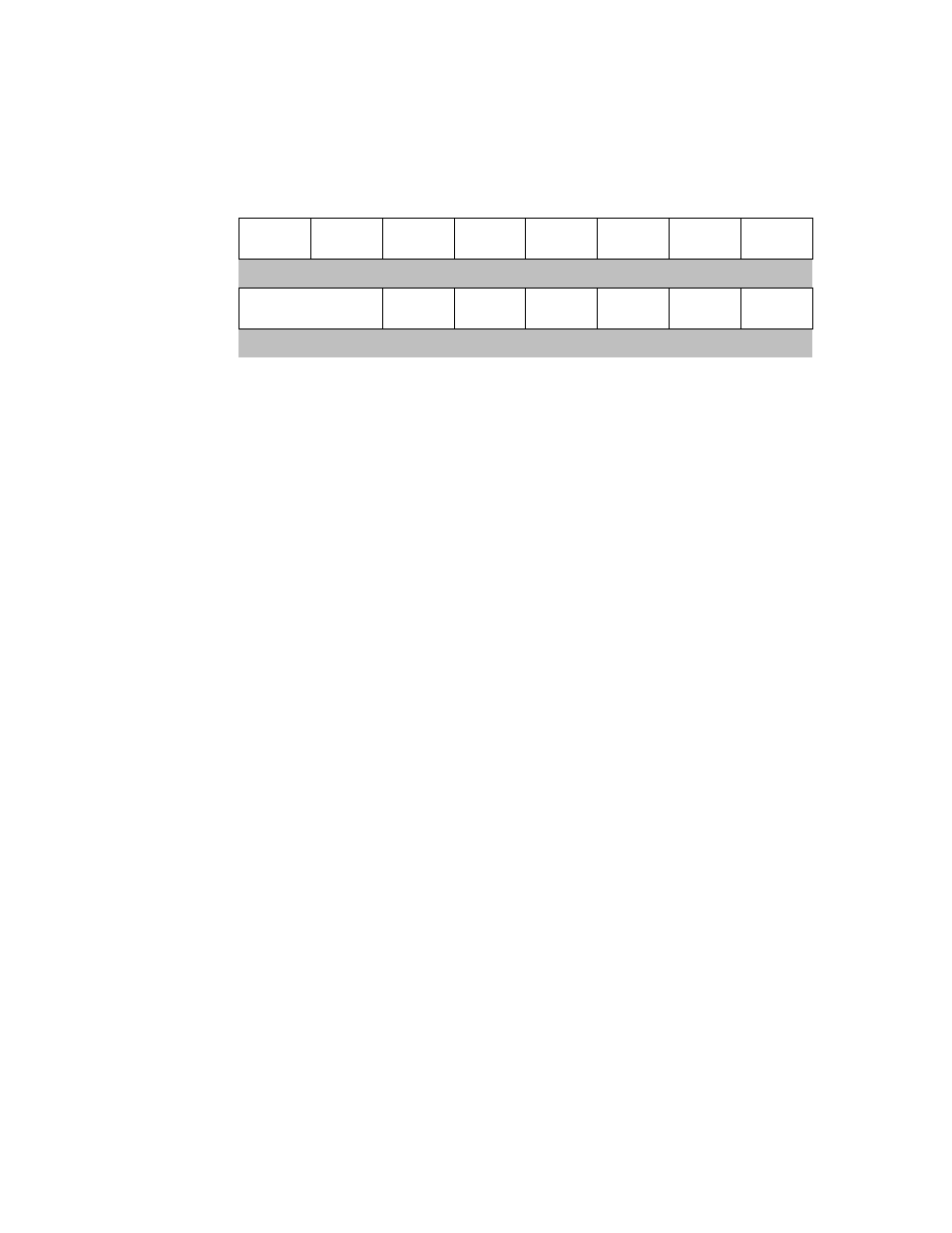

I/O SPACE - BANK1

OFFSET

NAME

TYPE

SYMBOL

2

BASE ADDRESS REGISTER

READ/WRITE

BAR

For ISA mode only, this register holds the I/O address decode option chosen for the I/O and ROM space. It

is part of the EEPROM saved setup, and is not usually modified during run-time. NOTE: This register

should ONLY be used in ISA mode. In PCMCIA mode, this register is read only.

HIGH

BYTE

A15

A14

A13

A9

A8

A7

A6

A5

0

0

0

1

1

0

0

0

LOW

BYTE

ROM SIZE

RA18

RA17

RA16

RA15

RA14

0

1

1

0

0

1

1

1

A15 - A13 and A9 - A5 - These bits are compared

in ISA mode against the I/O address on the bus to

determine the IOBASE for SMC91C95 registers.

The 64k I/O space is fully decoded by the

SMC91C95 down to a 16 location space, therefore

the unspecified address lines A4, A10, A11 and

A12 must be all zeros.

ROM SIZE - Determines the ROM decode area in

ISA mode memory space as follows:

00 = ROM disable

01 = 16k: RA14-18 define ROM select

10 = 32k: RA15-18 define ROM select

11 = 64k: RA16-18 define ROM select

RA18-RA14 - These bits are compared in ISA

mode against the memory address on the bus to

determine if the ROM is being accessed, as a

function of the ROM SIZE. ROM accesses are

read only memory accesses defined by nMEMRD

going low.

For a full decode of the address space unspecified

upper address lines have to be:

A19 = "1", A20-A23 lines are not directly

decoded, however ISA systems will only

activate nMEMRD only when A20-A23=0.

All bits in this register are loaded from the serial

EEPROM in ISA Mode only. In PCMCIA mode,

the I/O base is set to the default value (as in ISA

mode) as defined below.

The I/O base decode defaults to 300h (namely, the

high byte defaults to 18h). ROM SIZE defaults to

01. ROM decode defaults to CC000 (namely the

low byte defaults to 67h).