SMC Networks SMC91C95 User Manual

Page 37

37

I/O SPACE

(ISA and PCMCIA Mode)

In ISA mode, the base I/O space is determined by

the IOS0-IOS2 inputs and the EEPROM contents.

A4-A15 are compared against the base I/O

address for I/O space accesses.

In PCMCIA mode nREG (along with nIORD or

nIOWR) defines an I/O access regardless of the

A4-A15 value.

To limit the I/O space requirements to 16 locations,

the registers are assigned to different banks. The

last word of the I/O area is shared by all banks and

can be used to change the bank in use.

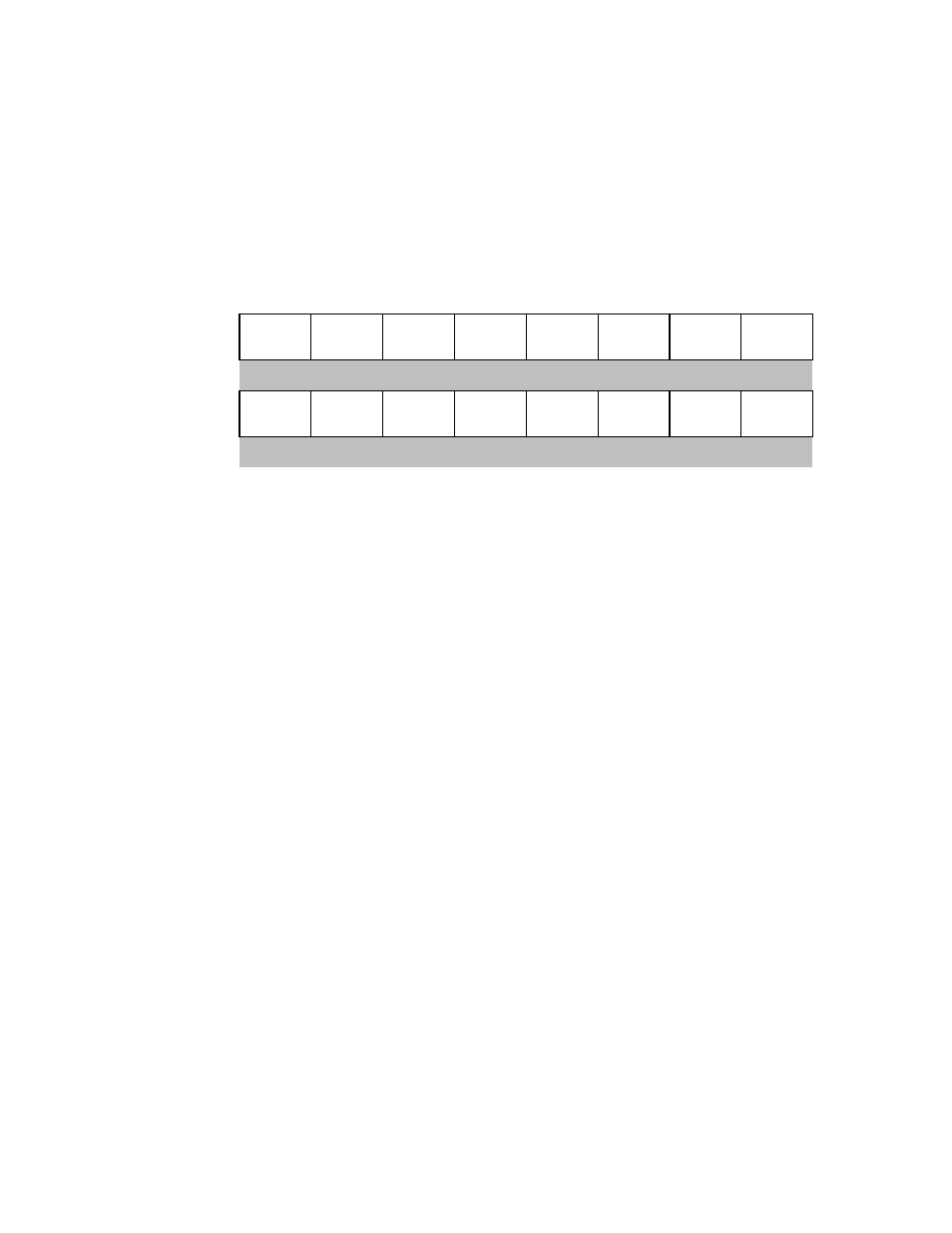

Registers are described using the following

convention:

OFFSET

NAME

TYPE

SYMBOL

HIGH

BYTE

bit 15

bit 14

bit 13

bit 12

bit 11

bit 10

bit 9

bit 8

X

X

X

X

X

X

X

X

LOW

BYTE

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

X

X

X

X

X

X

X

X

OFFSET - Defines the address offset within the

IOBASE where the register can be accessed at,

provided the bank select has the appropriate value.

The offset specifies the address of the even byte

(bits 0-7) or the address of the complete word.

The odd byte can be accessed using address

(offset + 1).

Some registers (like the Interrupt Ack., or like

Interrupt Mask) are functionally described as two

eight bit registers; in that case the offset of each

one is independently specified.

Regardless of the functional description, when the

SMC91C95 is in 16 bit mode, all registers can be

accessed as words or bytes.

The default bit values upon hard reset are

highlighted below each register.