Vme a24 status register – Spectrum Brands Quad C6x VME64 User Manual

Page 68

Monaco Technical Reference

Spectrum Signal Processing

Registers

56

Part Number 500-00191

Revision 2.00

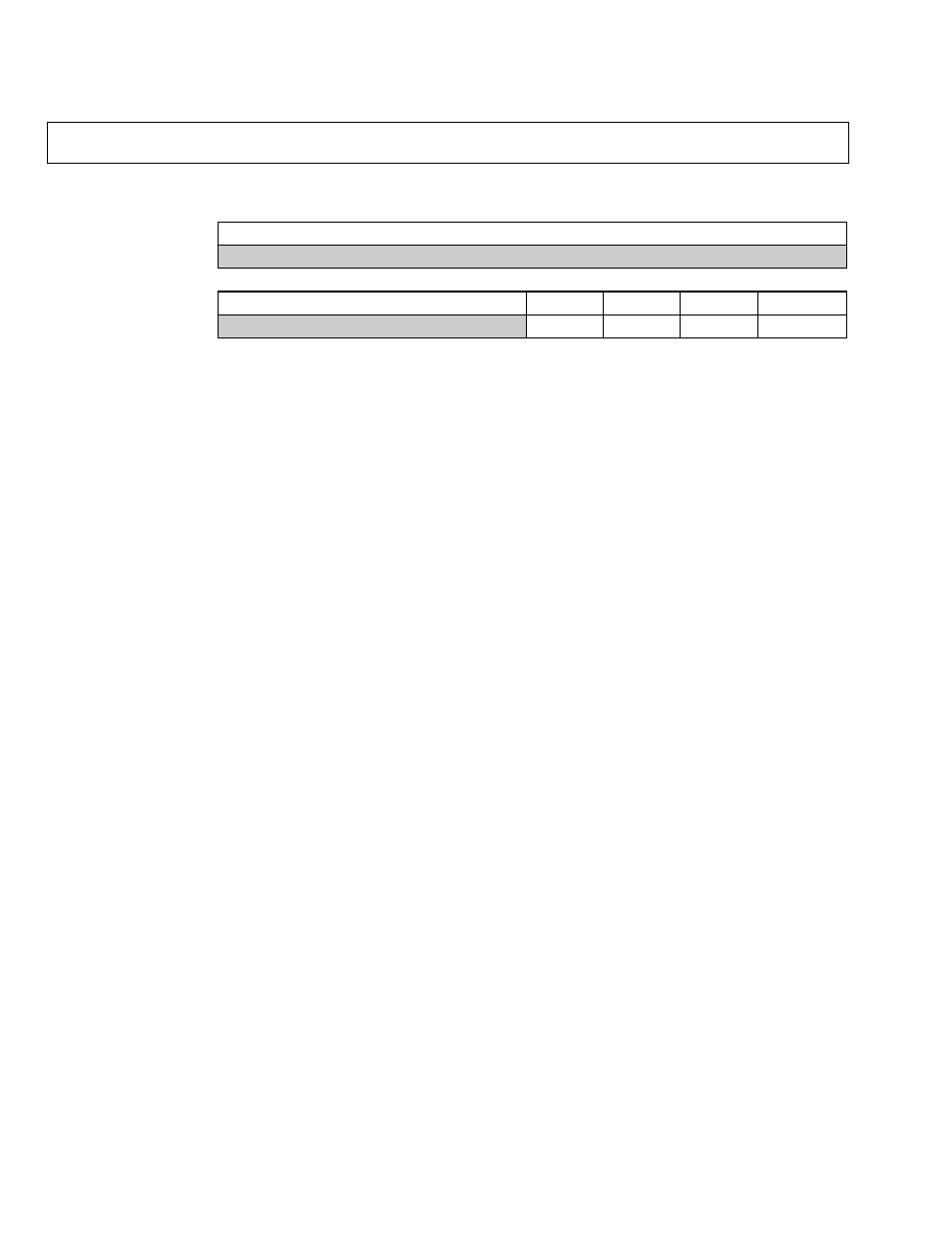

VME A24 Status Register

VME A24 Secondary Base Address + 1000h

D31..

..D8

Reserved

D7..

..D4

D3

D2

D1

D0

Reserved

HINT_D

HINT_C

HINT_B

HINT_A

The VME host reads this register to determine the state of the HINT lines from each

processor node. Each bit corresponds to one of the four processor nodes. The state of the

bit is simply a reflection of the HINT bit value in the corresponding ‘C6x HPIC register.

A “1” in the bit position indicates that the corresponding ‘C6x processor has requested

an interrupt.

HINT_A

Bit D0 is set to “1” when node A is requesting a host interrupt.

HINT_B

Bit D1 is set to “1” when node B is requesting a host interrupt.

HINT_C

Bit D2 is set to “1” when node C is requesting a host interrupt.

HINT_D

Bit D3 is set to “1” when node D is requesting a host interrupt.

This read only register is accessed from the VME A24 bus. It is located at offset 1000h

from the base address set by jumper JP1 (A23..A17).