Address strobe control mode – Spectrum Brands Quad C6x VME64 User Manual

Page 42

Monaco Technical Reference

Spectrum Signal Processing

DSP~LINK3 Interface

30

Part Number 500-00191

Revision 2.00

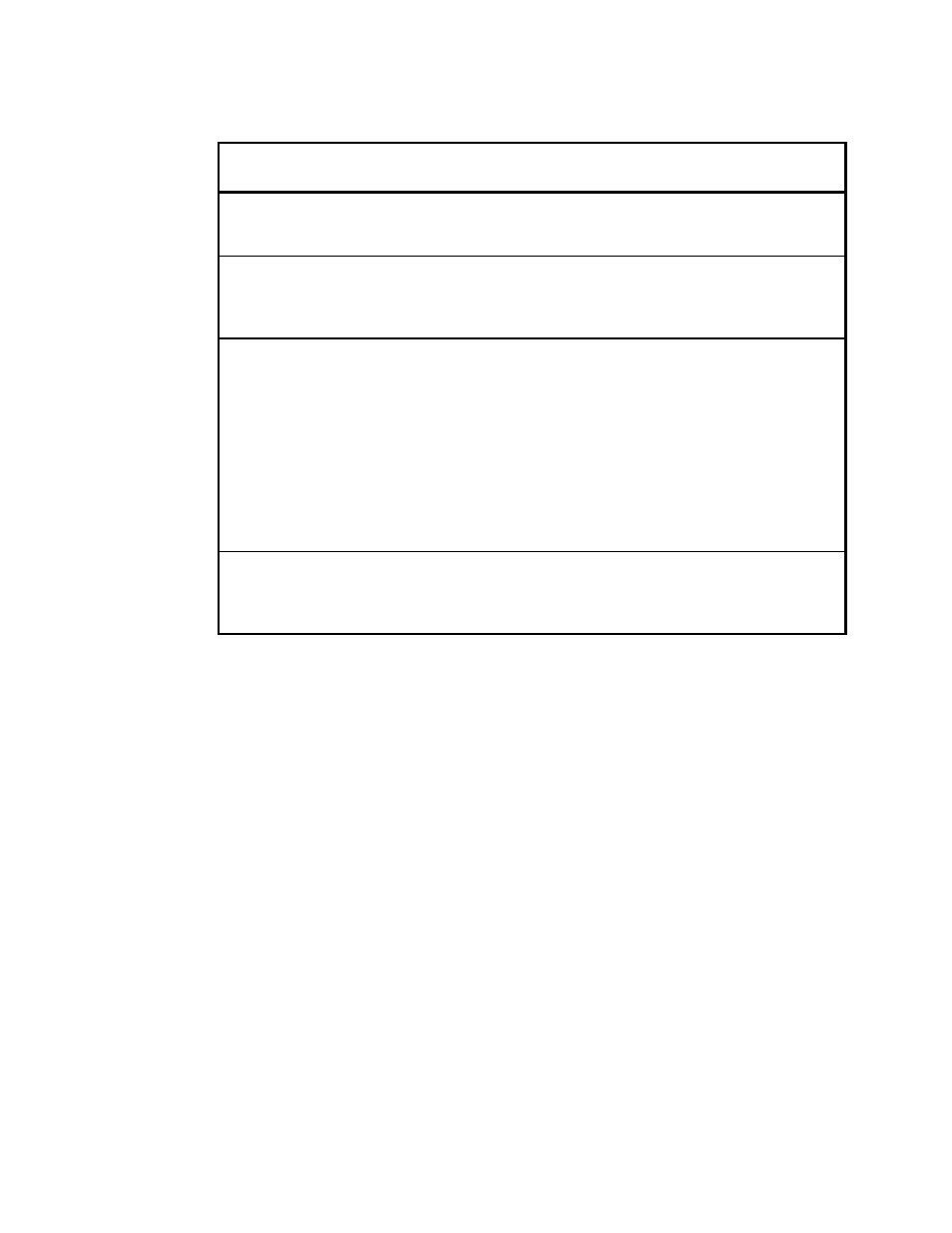

Table 10 DSP~LINK3 Data Transfer Operating Modes

Mode

Base

Address

ASTRB_EN

Bit

Description

Standard

Access

0160 0000h

x

For slave boards that are similar to DSP~LINK1

slave boards and operate with a fixed access

time.

Standard

Fast

Access

0164 0000h

0

For DSP~LINK3 slave boards that have fast,

fixed access time. This memory space is

shared with the Address Strobe Control

operating mode.

Address

Strobe

Control

0164 0000h

1

For slave boards that require more than the

16 KWords of addressing provided by the

standard DSP~LINK3 address lines. The bus

master uses the /ASTRB cycle to place the

page address onto the DSP~LINK3 data lines.

It determines which address page is accessed

on the slave board. This allows access to up to

2

14

address pages with each address page

having an address depth of 2

14

. The /ASTRB

Cycle has the same timing as the Standard

Fast transfer cycle.

Ready

Control

Access

0168 0000h

x

For DSP~LINK3 slave boards that require

variable length access times. /DSTRB is active

until the slave asserts the DSP~LINK3 ready

signal (/RDY) to end the cycle.

5.2.

Address Strobe Control Mode

The Address Strobe Control mode uses the same node A 64K address space as the

Standard Fast Access mode. The Address Strobe Control mode is enabled for this space

by setting bit D1, the ASTRB_EN bit, of the DSP~LINK3 register to “1”. This register is

located at address 016D 8018h of node A. Standard Fast Access mode writes will now

generate /ASTRB cycles. The DSP~LINK3 slave attached to the Monaco board should

then latch the lower addresses.