Single cycle bus access, Burst cycle bus access – Spectrum Brands Quad C6x VME64 User Manual

Page 32

Monaco Technical Reference

Spectrum Signal Processing

Global Shared Bus

20

Part Number 500-00191

Revision 2.00

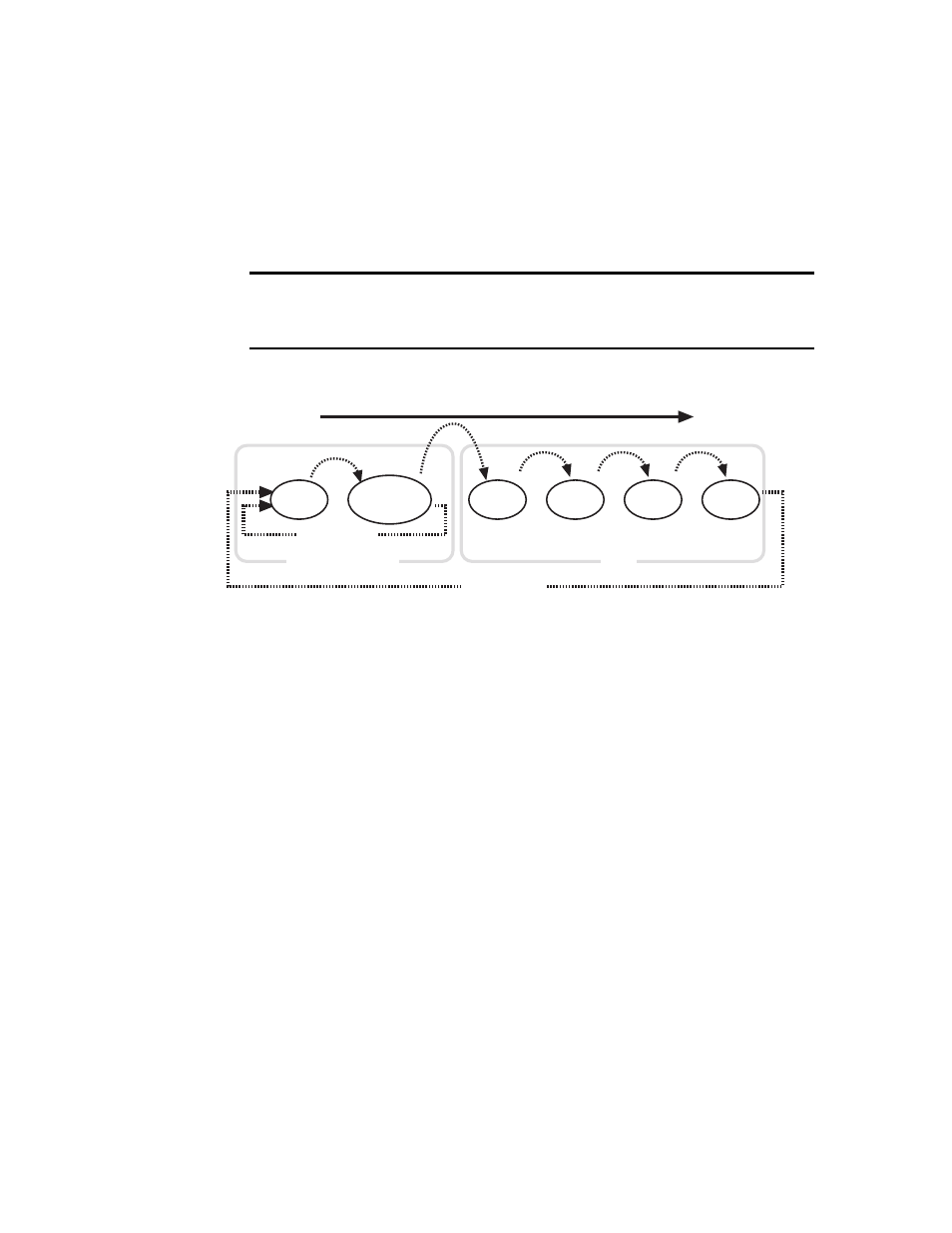

Bus ownership is cycled between the two highest priority devices (SCV64 and

Hurricane) until neither device requires the bus. Then the DSP Nodes are processed

round robin. After one pass through the DSP chain, the cycle loops back to include the

SCV64 and Hurricane. This eliminates any arbitration latency as bus ownership is

transferred between devices, and grants the highest priority to those devices interfacing

to external buses (VME and PCI), which require the fastest response. The arbitration

cycle is shown in the following figure.

Note:

Because there is no ownership timer for either Hurricane or SCV64 chip

the system designer must ensure that processors are not held off from the shared

resources for unreasonable lengths of time.

Access to the Global Shared Bus can use single, burst, or locked cycles.

3.2.1. Single Cycle Bus Access

For single cycle accesses a device requests the global shared bus by simply initiating a

read or write access to the bus. When the bus is free, the device acquires it and performs

the single cycle access. The bus is then released.

3.2.2. Burst Cycle Bus Access

Burst cycles are used during DMA transfers from a ‘C6x processor to the Global Shared

Bus. A 6-bit bus ownership timer on each node prevents a ‘C6x from owning the bus for

more than 640 ns when another device is requesting the bus. When the burst cycles are

begun, the timer is started. If another device requests the bus when the timer expires, the

bus is released; otherwise ownership is maintained and the timer is reset and started

again.

If multiple DSPs request the bus, this scheme allocates time to them fairly so that none

are locked out.

Highest Priority

Lowest priority

Round Robin

Round Robin

DSP

VME & PCI Bus

Node A

Hurricane

SCV64

Node D

Node C

Node B

Figure 7 Global Bus Arbitration