Interface processor l series – Sony MK7807V1 User Manual

Page 96

Specifications

Inputs/outputs

Analog audio inputs:

AUDIO IN connectors (Phoenix type

6-pin)

(2; 4 channels -2 stereo pairs)

Input level:

+ 4 dBm (600

Ω

/20 k

Ω

selectable,

balanced)

Reference input:

REF VIDEO/WORD CLOCK IN

connector

(BNC type) (1)

Video input:

0.3 Vp-p (525/29.9 Hz, 625/25 Hz,

1125/60 Hz)

Word sync:

0.5 to 5.0 Vp-p (48 kHz)

Input return loss:

40 dB or more (at 5 MHz, 75

Ω

terminated)

AES/EBU audio outputs:

AES/EBU OUT connectors (BNC type)

(2; 1 for each stereo pair)

1.0 Vp-p

؎10%, 75

Ω

Output return loss:

25 dB or more (at 0.1 MHz to 6.0 MHz)

Rise time/fall time:

30 to 44 ns

Alignment jitter:

Less than

؎20 nsp-p

DC offset:

Less than 0

؎50 mV

Reference output:

Passive loop-through output connector

(selectable to Word Clock output

connector)

(BNC type) (1)

Word sync output:

1.0 Vp-p or 2.8 Vp-p, 48 kHz

Video characteristics

Sampling frequency:

48 kHz

Resolution:

24 bits

Head room:

20 dB (at +4 dBm)

Channel coding:

AES/EBU format

Frequency response:

Within +0.1/-0.2 dB (20 Hz to 20 kHz)

Distortion:

Less than 0.02%

Signal to noise ratio:

103 dB or more

Crosstalk:

Less than -90 dB (at under 15 kHz)

CMRR (Common Mode Rejection Ratio):

More than 80 dB (at 60 Hz)

Phase difference between channels:

Less than 4° (at 1 kHz)

Encoding delay:

Approx. 0.9 ms

General

Power requirements:

+ 5 V DC: 1.1 A (supplied from the

PFV-L Series Interface Unit)

Operating temperature:

5 to 40 °C (41 to 104 °F)

Operating humidity:

10 to 90% (no condensation)

Dimensions

Board (H x D):

77 x 267 mm

(3 1/8 x 10 5/8 inches)

Connector panel (W x H):

33 x 85 mm

(1 5/16 x 3 3/8 inches)

Mass

Board:

160 g (6 oz)

Connector panel:

110 g (4 oz)

Service parts: Extension board (Part

No.A-8322-598-A), Maintenance manual

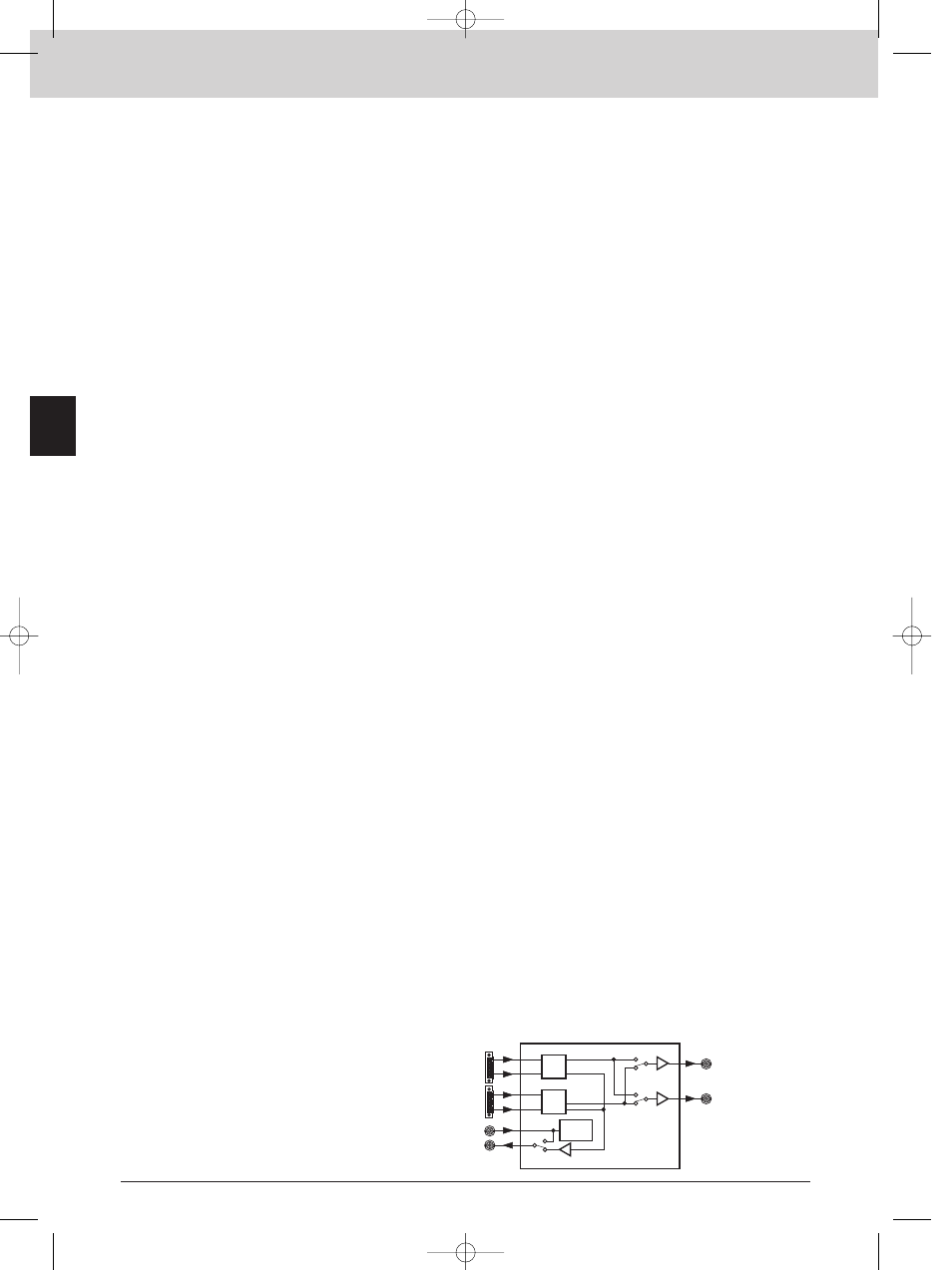

AES/EBU OUT 1

AES/EBU OUT 2

AUDIO IN CH-1

AUDIO IN CH-2

AUDIO IN CH-3

AUDIO IN CH-4

REF IN

CLOCK

GEN.

LOOP-THROUGH

or WORD CLOCK OUT

ADC

ADC

94

Inter

face Pr

ocessor L Series

Interface Processor L Series

*SGC_0069-0098 02.3.16 5:03 PM Page 94