Intel ARCHITECTURE IA-32 User Manual

Page 529

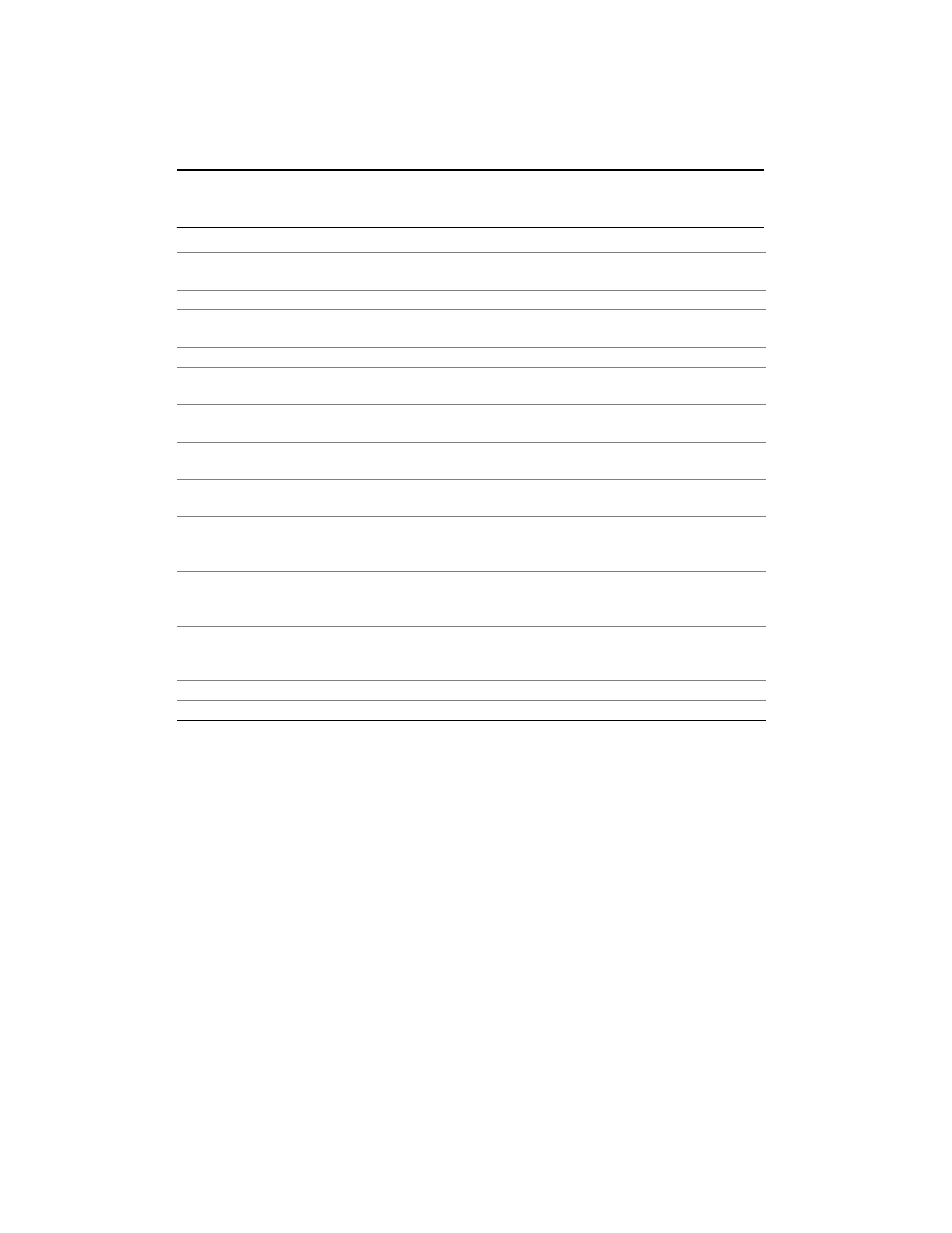

IA-32 Instruction Latency and Throughput

C

C-15

PCMPGTB/PCMPGTD/

PCMPGTW mm, mm

2

2

1

1

MMX_ALU

PMADDWD

3

mm, mm

9

8

1

1

FP_MUL

PMULHW/PMULLW

3

mm, mm

9

8

1

1

FP_MUL

POR mm, mm

2

2

1

1

MMX_ALU

PSLLQ/PSLLW/

PSLLD mm, mm/imm8

2

2

1

1

MMX_SHFT

PSRAW/PSRAD mm,

mm/imm8

2

2

1

1

MMX_SHFT

PSRLQ/PSRLW/PSRLD

mm, mm/imm8

2

2

1

1

MMX_SHFT

PSUBB/PSUBW/PSUBD

mm, mm

2

2

1

1

MMX_ALU

PSUBSB/PSUBSW/PSU

BUSB/PSUBUSW mm,

mm

2

2

1

1

MMX_ALU

PUNPCKHBW/PUNPCK

HWD/PUNPCKHDQ

mm, mm

2

2

1

1

MMX_SHFT

PUNPCKLBW/PUNPCK

LWD/PUNPCKLDQ mm,

mm

2

2

1

1

MMX_SHFT

PXOR mm, mm

2

2

1

1

MMX_ALU

EMMS

1

12

12

Table C-6

MMX Technology 64-bit Instructions (continued)

Instruction

Latency

1

Throughput

Execution Unit

2