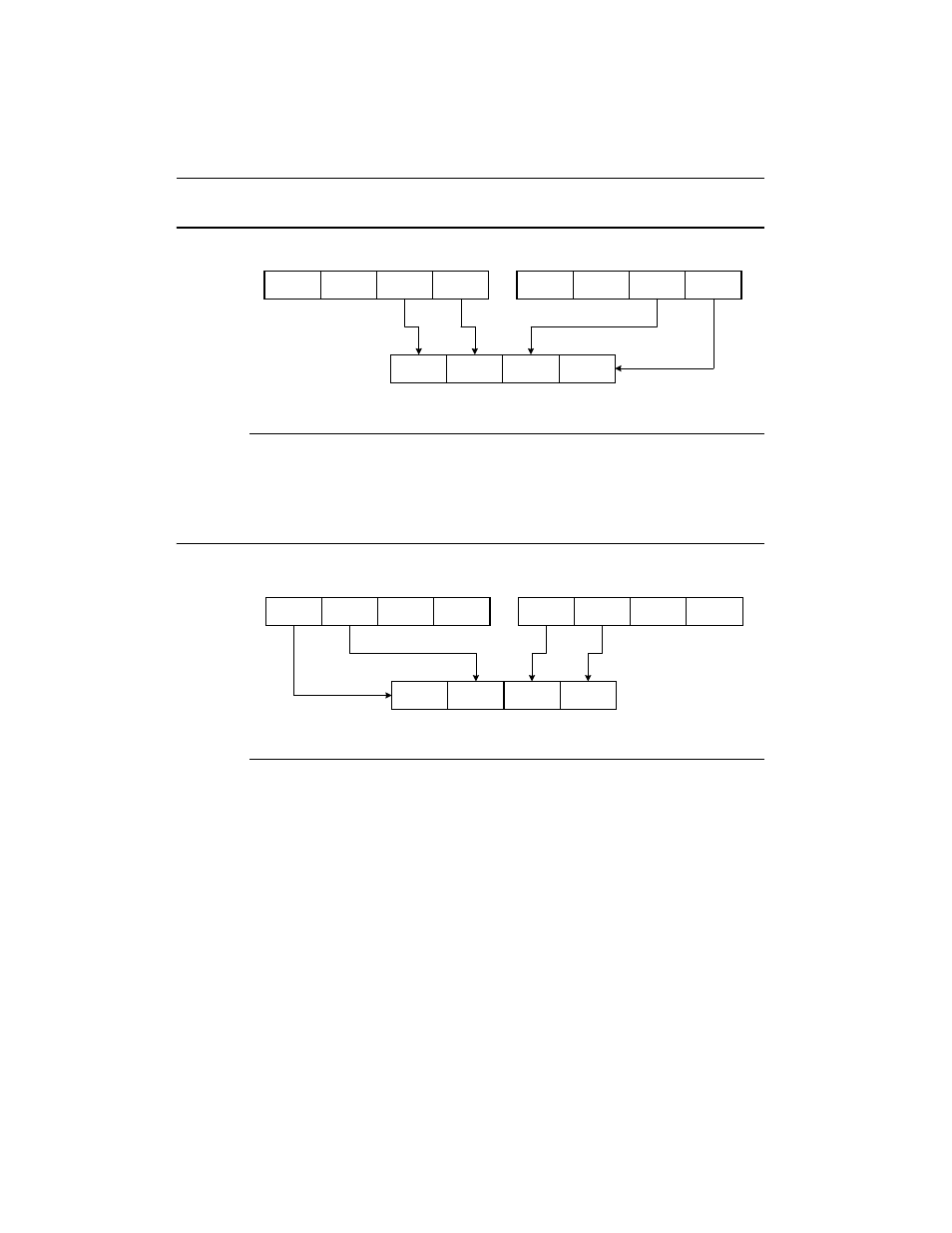

Figure 4-4, Result of non-interleaved unpack high in mm1 -12, Figure 4-3 – Intel ARCHITECTURE IA-32 User Manual

Page 232: Result of non-interleaved unpack low in mm0 -12

IA-32 Intel® Architecture Optimization

4-12

The other destination register will contain the opposite combination

illustrated in Figure 4-4.

Code in the Example 4-6 unpacks two packed-word sources in a

non-interleaved way. The goal is to use the instruction which unpacks

doublewords to a quadword, instead of using the instruction which

unpacks words to doublewords.

Figure 4-3

Result of Non-Interleaved Unpack Low in MM0

Figure 4-4

Result of Non-Interleaved Unpack High in MM1

O M15161

2

1

2

0

1

1

1

0

m m /m 64

m m

m m

2

3

2

2

2

1

2

0

1

3

1

2

1

1

1

0

O M15162

2

3

2

2

1

3

1

2

m m /m 64

m m

m m

2

3

2

2

2

1

2

0

1

3

1

2

1

1

1

0