Communication processor module initialization, I/o port initialization, Cpm rccr reset – Interphase Tech 4538 User Manual

Page 89

Chapter 2: 4538 Power-Up Initialization

4538 Hardware Reference Manual

67

The instruction and data caches are enabled through bits ICE and DCE of register HID0

respectively. The setting of ICE bit must be preceded by an

isync

instruction. The setting

of DCE bit must be preceded by a

sync

instruction.

Communication Processor Module Initialization

I/O Port Initialization

The CPM I/O ports have to be configured according to their usage (see

Processor Module (CPM) I/O Ports on page 8

). In the Interphase boot firmware, this is

done during the early phase of the boot (in

startup.asm

).

Each CPM port is set by four registers in the Internal Register Area: PDIRx, PPARx,

PODRx, and PDATx.

CPM RCCR Reset

At boot, it is important to reset the RISC Controller Configuration Register (RCCR) in

order to disable any previously loaded CPM microcode and start with the known default

CPM microcode.

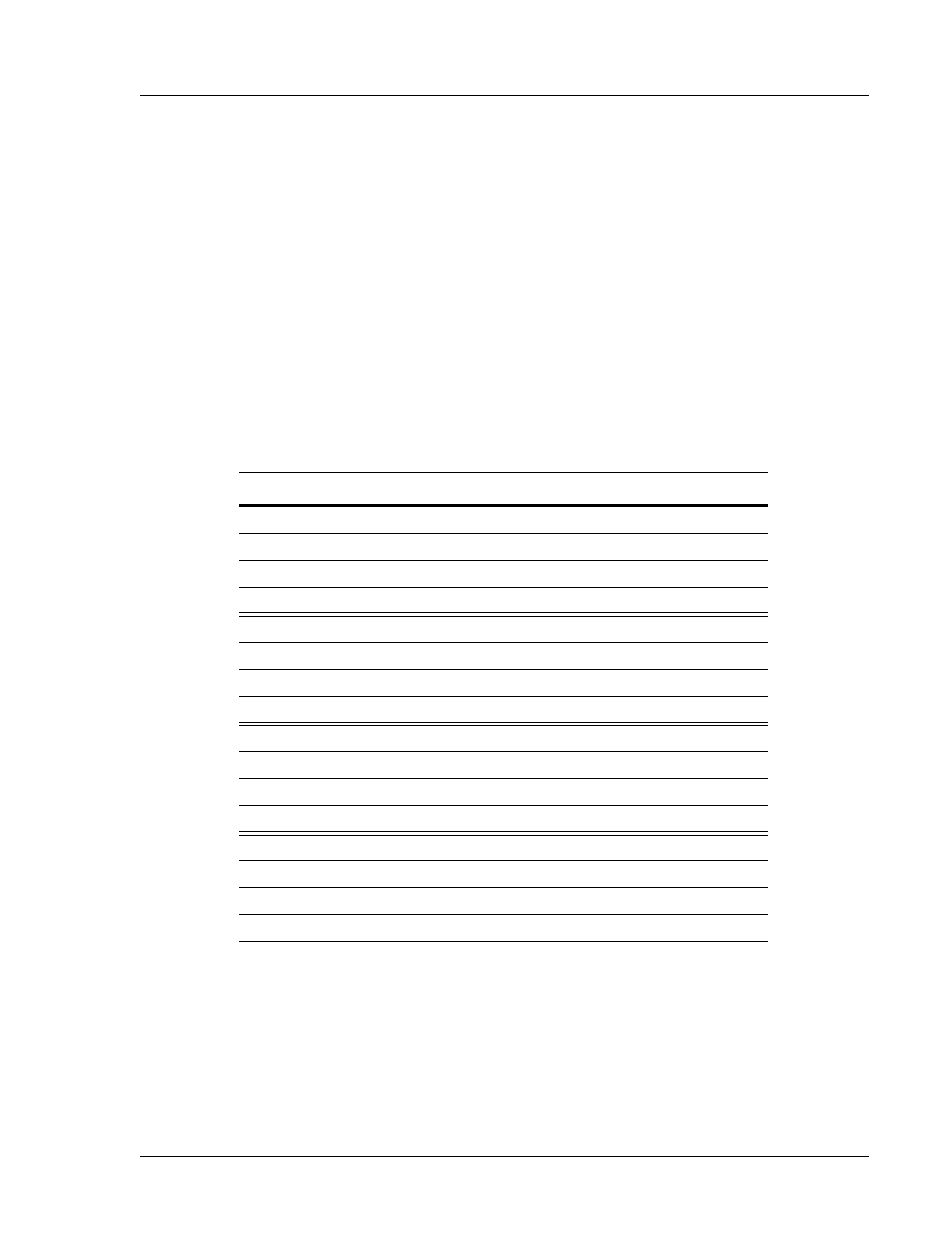

Table 2-3. CPM Port Register initialization Values

Register

Address

Init. Value

Comment

33$5$ [))' [

3625$ [))' [

3'$7$ [))' [ 6:02'(B1 &20&/.B1

3',5$ [))' [)')))))

33$5% [))' [

3625% [))' [

3'$7% [))' [

3',5% [))' [

33$5& [))' [

3625& [))' [

3'$7& [))' [ 4XDG)DOF (WKHUQHW UHVHW GHDFWLYDWHG

3',5& [))' [)))))&$

33$5' [))' [

3625' [))' [

3'$7' [))' [ /('V RII

3',5' [))' [))