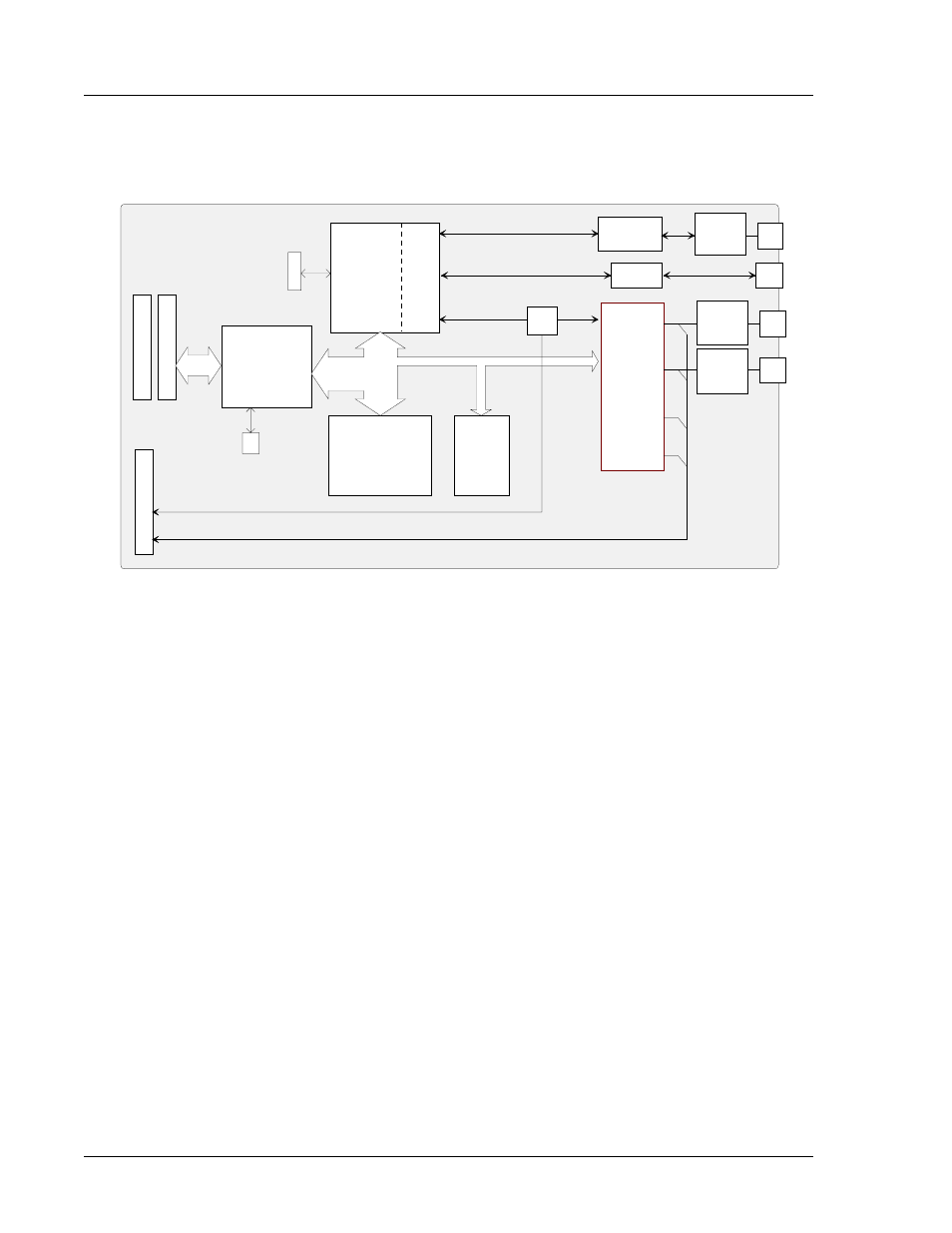

4538 hardware structure, The powerquicc ii, Figure 1-1 – Interphase Tech 4538 User Manual

Page 24: 4538 structure

The PowerQUICC II

2

Interphase Corporation

4538 Hardware Structure

shows the 4538 hardware structure:

Figure 1-1. 4538 Structure

The PowerQUICC II

The local CPU is a Motorola MPC8260 RISC embedded processor. The MPC8260

includes three major parts:

• An MPC603e core

• A System Interface Unit (SIU)

• A Communication Processor Module (CPM)

The MPC603e core is derived from the PowerPC™ 603e core and includes mainly the

integer core and the 16 KB data and 16 KB instruction caches.

The SIU includes a memory management unit and enables control of the external 60x local

bus (64-bit data width). The SIU also provides a local bus (32-bit data, 32-bit internal/18-

bit external address) used to enhance the operation of the Fast Communication Controllers

(FCCs). It can be used to store connection tables for ATM, buffer descriptors, or raw data

that is transmitted between channels. It is synchronized with the 60x bus and runs at the

same frequency. The 4538 does not provide CPM local memories.

The Communication Processor Module (CPM) is a super-set of the PowerQUICC II CPM

with additional capabilities. It features:

• Two Multichannel Communications Controllers (MCCs)

3RZHU63$1

3&,

%ULGJH

%#Ãiv

%#ÃH7

T9S6H

3&,

%XV

9rryrÃ

Q

Q!

UT6

TH8Ã

03&

!FiÃTr vhy

@@QSPH

/LQH

,)

#ÃH7

Ayhu

/LQH

,)

ÃÃÃ@ur r

U hprvr

HDD

@ U E

A hr

(-7

SE#'

SE#'

SE#$

/LQH

,)

Q#

ST!"!

U9H

Ã

ÃUU`

E68F

A hr Ã

A hr Ã!

A hr Ã"

A hr Г#

%Г7

E!

E

E#

E"