2 arbitration signals, 3 interrupt signal, 4 system signals – Intel 82540EP User Manual

Page 17: 5 error reporting signals, Arbitration signals, Interrupt signal, System signals, Error reporting signals

Networking Silicon — 82540EP

Datasheet

11

3.2.2

Arbitration Signals

3.2.3

Interrupt Signal

3.2.4

System Signals

3.2.5

Error Reporting Signals

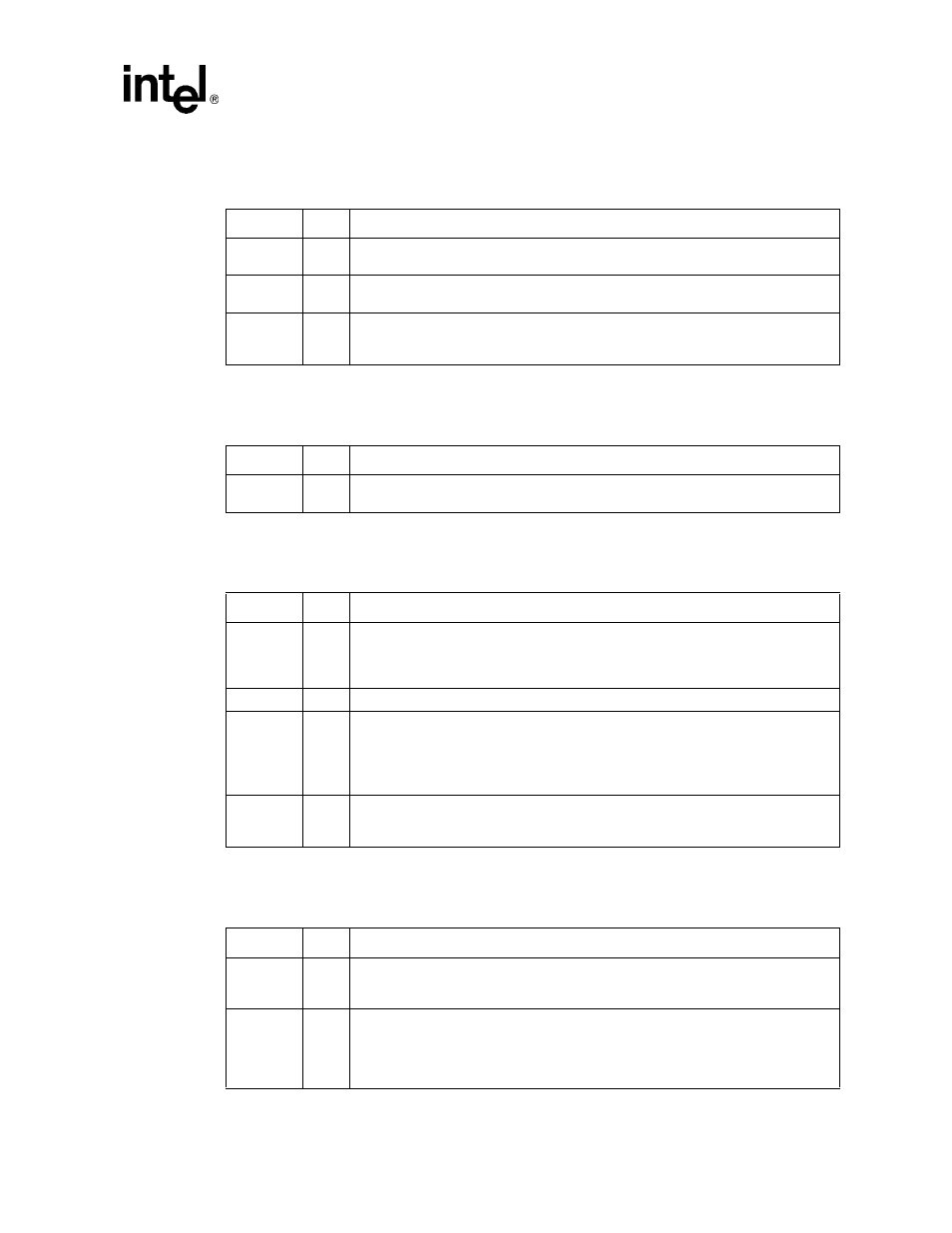

Symbol

Type

Name and Function

REQ#

TS

Request Bus.

The Request Bus signal is used to request control of the bus from the

arbiter. This signal is point-to-point.

GNT#

I

Grant Bus.

The Grant Bus signal notifies the 82540EP that bus access has been

granted. This is a point-to-point signal.

LOCK#

I

Lock Bus.

The Lock Bus signal is asserted by an initiator to require sole access to a

target memory device during two or more separate transfers. The 82540EP device

does not implement bus locking.

Symbol

Type

Name and Function

INTA#

TS

Interrupt A.

Interrupt A is used to request an interrupt by port 1 of the 82540EP. It is an

active low, level-triggered interrupt signal.

Symbol

Type

Name and Function

CLK

I

PCI Clock.

The PCI Clock signal provides timing for all transactions on the PCI bus and

is an input to the

82540EP

device. All other PCI signals, except the Interrupt A

(INTA#) and PCI Reset signal (RST#), are sampled on the rising edge of CLK. All other

timing parameters are defined with respect to this edge.

M66EN

I

66 MHz Enable.

M66EN indicates whether the system bus is enabled for 66MHz.

RST#

I

PCI Reset.

When the PCI Reset signal is asserted, all PCI output signals, except the

Power Management Event signal (PME#), are floated and all input signals are ignored.

The PME# context is preserved, depending on power management settings.

Most of the internal state of the 82540EP is reset on the de-assertion (rising edge) of

RST#.

CLKRUN#

I/O

OD

Clock Run.

This signal is used by the system to pause the PCI clock signal. It is used

by the 82540EP controller to request the PCI clock. When the CLKRUN# feature is

disabled, leave this pin unconnected.

Symbol

Type

Name and Function

SERR#

OD

System Error.

The System Error signal is used by the 82540EP controller to report

address parity errors. SERR# is open drain and is actively driven for a single PCI clock

when reporting the error.

PERR#

STS

Parity Error.

The Parity Error signal is used by the 82540EP controller to report data

parity errors during all PCI transactions except by a Special Cycle. PERR# is sustained

tri-state and must be driven active by the 82540EP controller two data clocks after a

data parity error is detected. The minimum duration of PERR# is one clock for each

data phase a data parity error is present.