Sundance SMT166 User Manual

Page 9

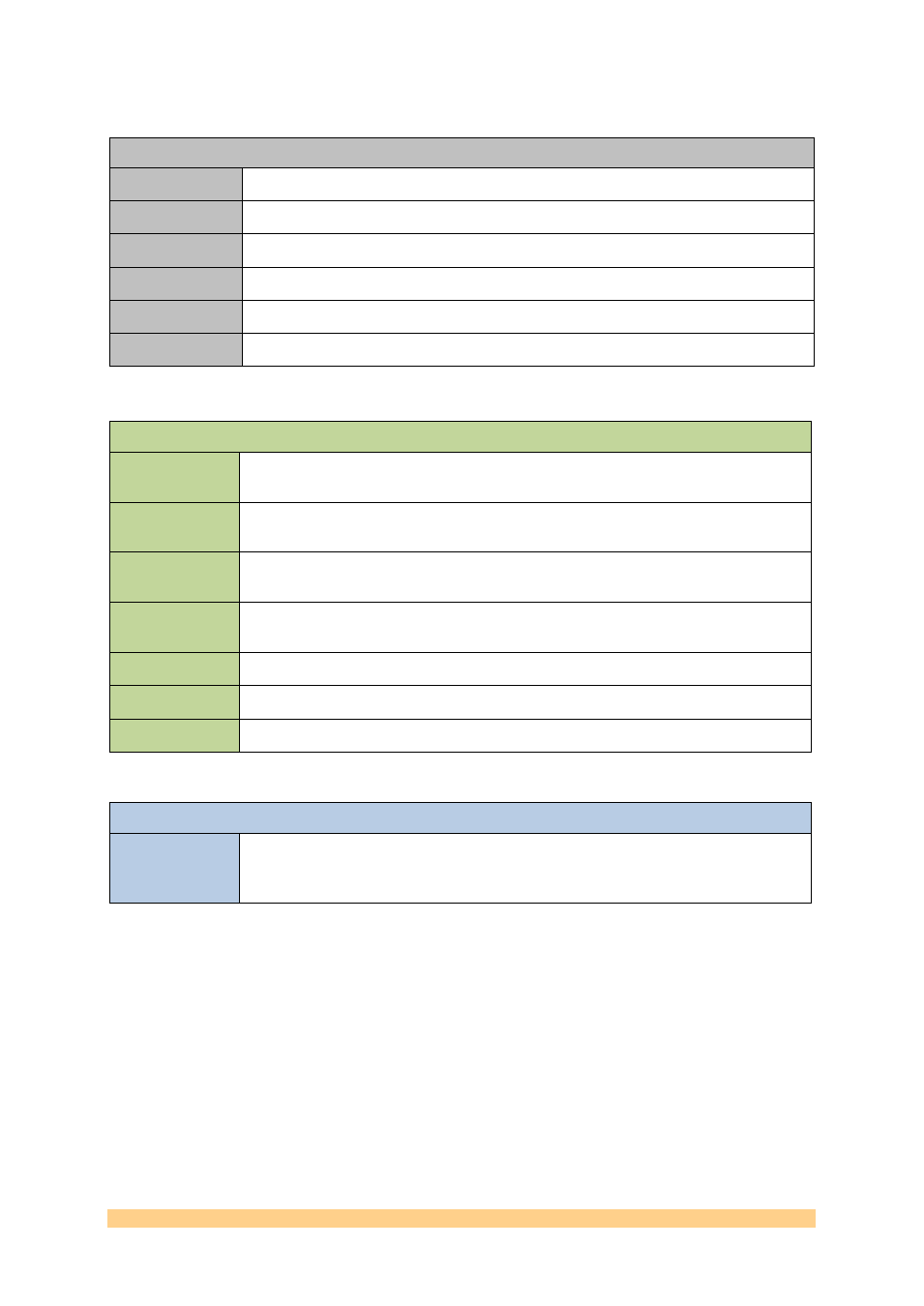

The tables below detail the SLB, RSL and Channel links:

SLB Links

i

Full SLB between FPGA0 and SLB site 0.

j

Full SLB between FPGA0 and SLB site 1.

k

Full SLB between FPGA1 and SLB site 2.

l

Full SLB between FPGA1 and SLB site 3.

m

Half SLB between FPGA0 and extra SLB connector.

n

Half SLB between FPGA1 and extra SLB connector.

RSL Links

i

Gen1 x1 express link between FPGA0 and 1-lane express

connector. Also carries a reference clock and a reset.

j

Gen1 x4 express link between FPGA0 and 4-lane express

connector. Also carries a reference clock and a reset.

k

Gen1 x1 express link between FPGA1 and 1-lane express

connector. Also carries a reference clock and a reset.

l

Gen1 x4 express link between FPGA1 and 4-lane express

connector. Also carries a reference clock and a reset.

m

x2 RSL link between FPGA0 and Master module.

n

x2 RSL link between FPGA1 and Master module.

o

x4 RSL link between FPGA0 and FPGA1.

Channel Links

i

One channel is defined as a 32-bit bus (unidirectional), a clock, a

write and a ready signal. Two channels are between the FPGA0 and

FPGA1.

Product Specification SMT166

Page 9 of 44

Last Edited: 17/06/2014 16:12:00