3 dip switch settings / fpga configuration – Sundance SMT166 User Manual

Page 19

4.2.3

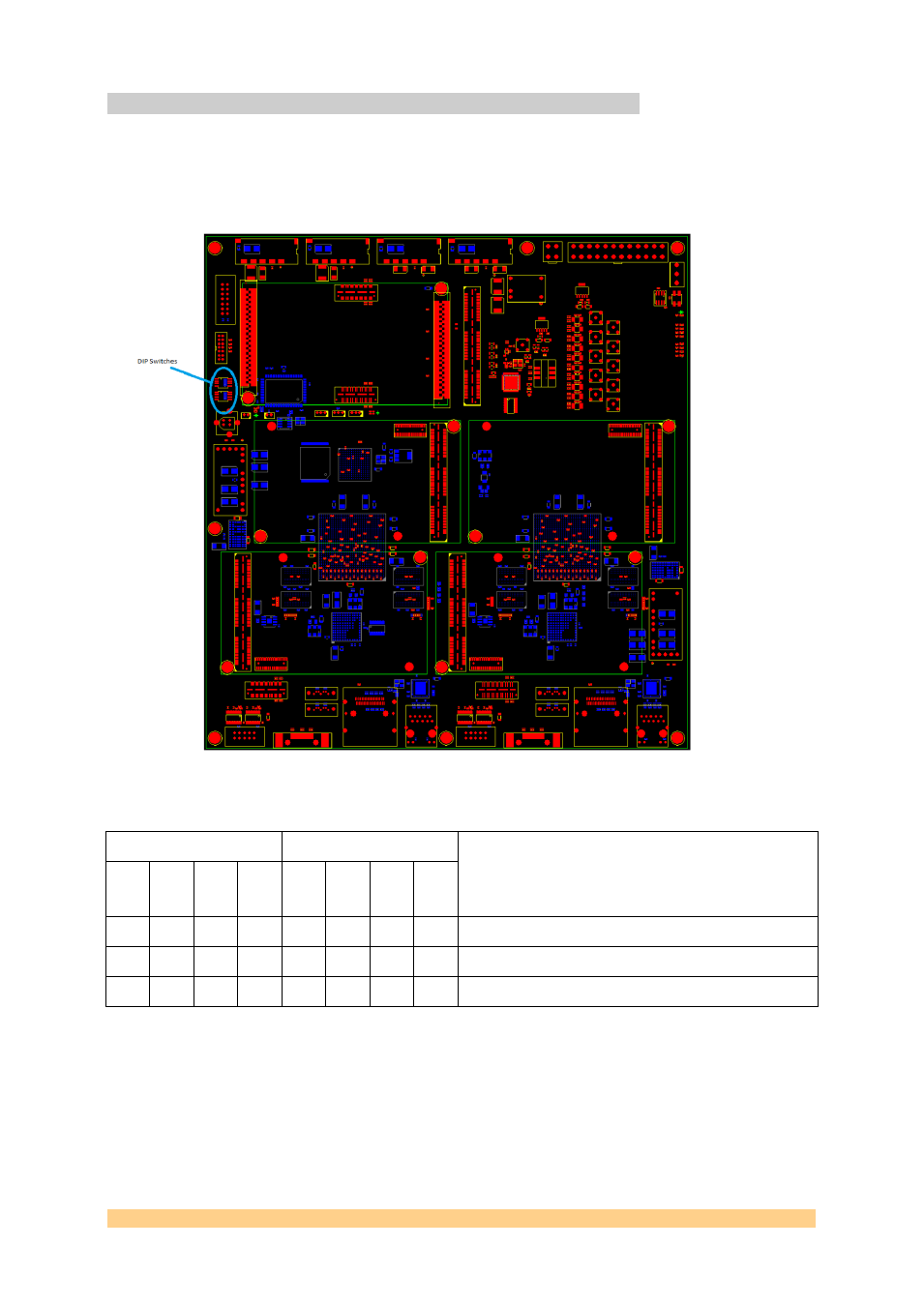

DIP Switch Settings / FPGA Configuration

When the board is powered up or the reset button pressed, the CPLD performs the

process of configuring the FPGAs. There are several options available as decided by

the DIP switch settings. These switches are located as shown here:

The following table shows the settings available:

SW3

SW2

Function

1

2

3

4

1

2

3

4

On Off Off Off On On Off Off SMT166 flash programming

Off Off Off Off On On Off Off TIM flash programming

Off Off Off Off On On On On Normal operation

The first setting (SMT166 flash programming) is used when the flash is required to

be programmed with FPGA bitstreams using Sundance’s SMT6002 flash

programming software package.

The second setting (TIM flash programming) allows the SMT6002 package to be able

to program the flash on the attached TIM (if present. See TIM user guide for details).

Product Specification SMT166

Page 19 of 44

Last Edited: 17/06/2014 16:12:00