Sundance SMT166 User Manual

Page 38

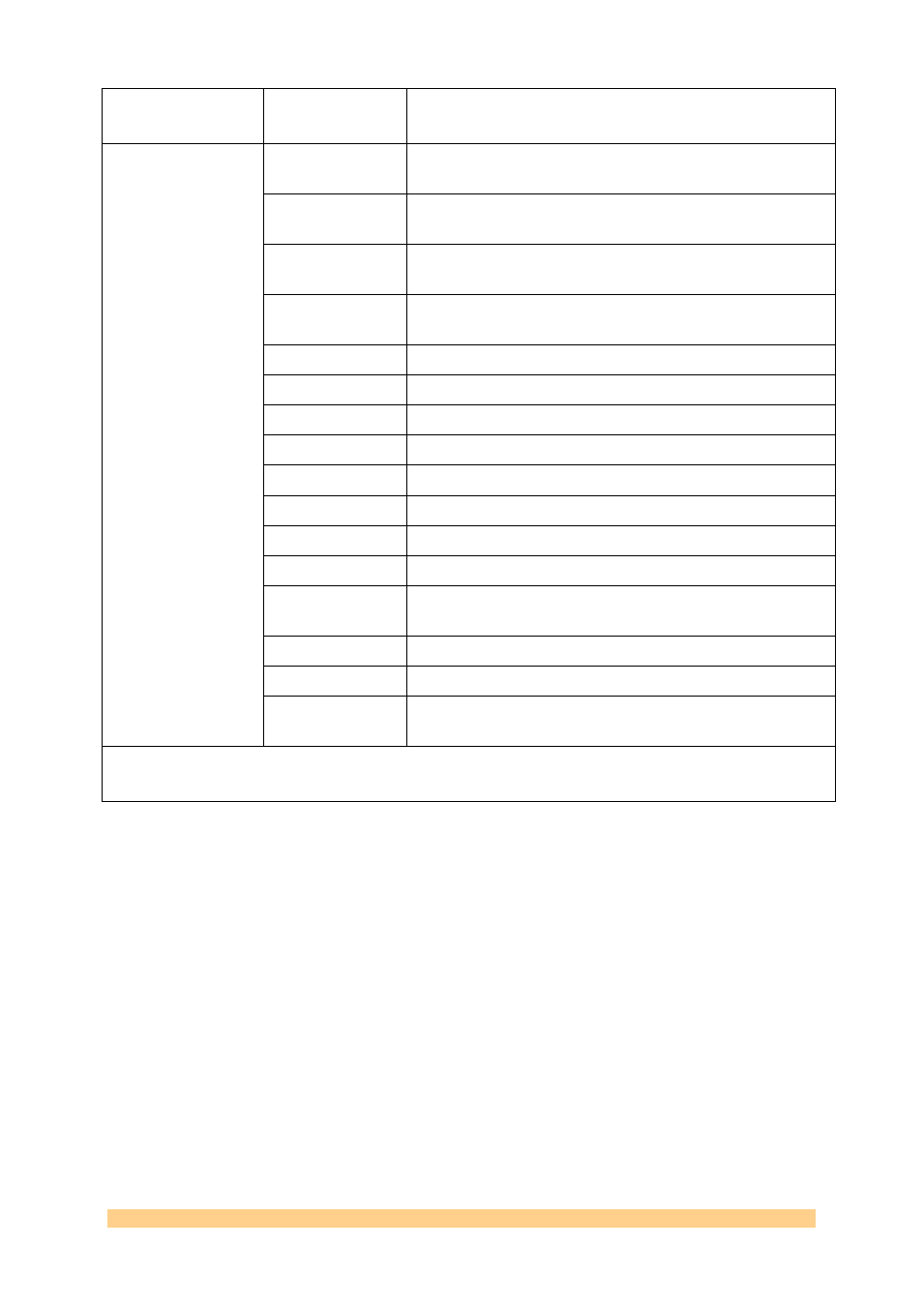

Interface

Signal / Bus

FPGA Pin #

SLB0

DAIP/N[0:7]

C20/D20 G21/G22 J20/J21 E22/E23 F19/F20

D21/E21 H22/J22 K21/K22

DBIP/N[0:7]

A23/A24 B23/C23 B21/B22 A20/A21 H19/H20

E19/D19 A18/A19 B18/C18

DAQP/N[0:7]

C32/B32 E32/E33 A33/B33 C33/B34 D34/C34

E34/F34 H34/H33 K33/J34

DBQP/N[0:7]

J26/J27 F30/G30 G31/H30 K28/J29 F31/E31

J30/K29 D31/D32 G32/H32

CKOUTIP/N

B20/C19

CKOUTQP/N

F21/G20

RSLCLKP/N

K26/K27

SYSCLKP/N

F33/G33

DooRIP/N

L20/L21

DooRQP/N

L25/L26

ExtTrigIP/N

C22/D22

ExtTrigQP/N

J31/J32

SIGNAL[0:11]

G26 B27 D24 C28 C29 F25 G27 C27 E24 B28 D29

G25

CNTRL[0:8]

E26 B25 F26 A25 H27 A28 F28 G28 A29

SMB

CLK:D25 DATA:D26 ALERT:C24

Misc

SerNum:C25 PSEN0:D27 PSEN1:E27 MODE0:B26

MODE1:A26

DooR is Data out of Range.

Two independent channels I and Q.

Product Specification SMT166

Page 38 of 44

Last Edited: 17/06/2014 16:12:00

- SMT107 (16 pages)

- SMT6035 v.2.2 (39 pages)

- SMT6012 v.4.6 (22 pages)

- FC100 (12 pages)

- FC108 v.1.1 (10 pages)

- SMT6065 v.4.0 (45 pages)

- FFT v.2.1 (19 pages)

- SMT111 (18 pages)

- SMT118LT (10 pages)

- SMT118 (20 pages)

- SMT123-SHB (13 pages)

- SMT128 (15 pages)

- SMT145 (18 pages)

- SMT148 (35 pages)

- SMT130 v.1.0 (46 pages)

- SMT148FX (48 pages)

- SMT310Q (55 pages)

- PARS (70 pages)

- SMT166-FMC (52 pages)

- SMT300Q v.1.6 (61 pages)

- SMT310 v.1.6 (50 pages)

- SMT317 (24 pages)

- SMT326v2 (24 pages)

- SMT338 (19 pages)

- SMT349 (32 pages)

- SMT339 v.1.3 (27 pages)

- SMT338-VP (22 pages)

- SMT358 (25 pages)

- SMT351T (37 pages)

- SMT351 (25 pages)

- SMT350 (45 pages)

- SMT362 (30 pages)

- SMT365G (23 pages)

- SMT364 (37 pages)

- SMT373 (15 pages)

- SMT368 (24 pages)

- SMT370v3 (46 pages)

- SMT377 (22 pages)

- SMT381 2007 (31 pages)

- SMT381-VP (81 pages)

- SMT387 (42 pages)

- SMT391 (18 pages)

- SMT384 (47 pages)

- SMT390-VP (55 pages)