Sundance SMT166 User Manual

Page 40

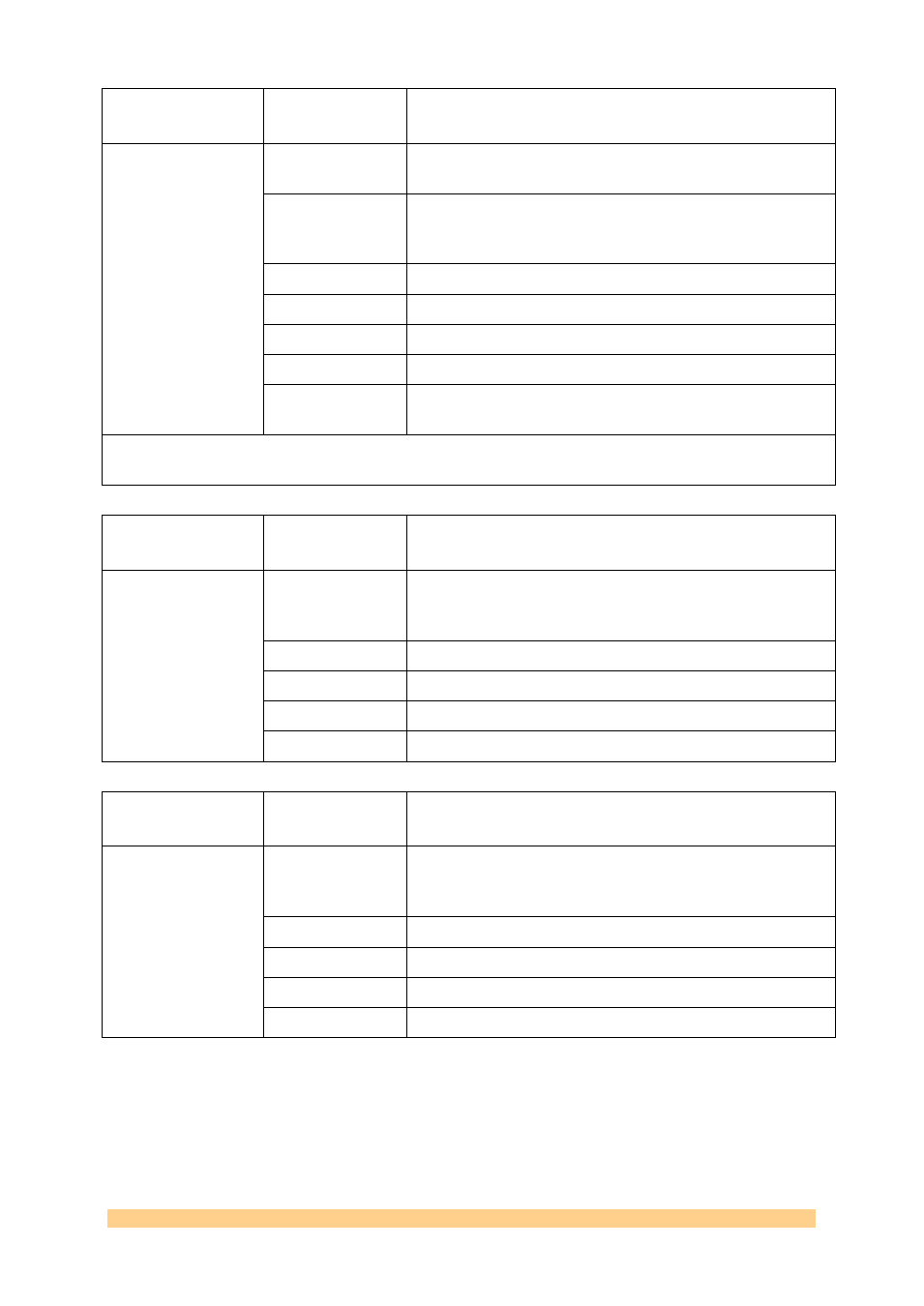

Interface

Signal / Bus

FPGA Pin #

Half SLB

DAP/N[0:7]

AA34/AA33 AD34/AC34 AC33/AB33 AA25/Y26

AE34/AF34 AB32/AC32 AD32/AE32 AG33/AG32

DBP/N[0:7]

AA30/AA31 AB30/AB31 AE31/AD31

AA28/AA29 AD29/AC29 AB28/AC28

AB27/AC27 AA26/AB26

CKOUTP/N

AD30/AC30

CLKP/N

AE33/AF33

DooRP/N

AG31/AF31

ExtTrigP/N

AB25/AC25

CNTRL[0:14]

AD22 AC22 AC24 AC23 AE22 AE23 AB23 AA23

AG23 AF23 AA24 Y24 G23 H23 N24

The Half SLB interface uses the Q data bus section for FPGA1 and the I section for

FPGA2.

Interface

Signal / Bus

FPGA Pin #

Channel 0

Data[0:31]

M31 L31 N25 M25 K32 K31 M26 M27 P31 P30

N27 P27 L33 M32 L28 M28 P25 P26 R28 R27 R31

R32 R26 T26 K34 L34 M30 N30 N34 P34 P29 R29

Clock

N28

Write

N29

CE

M33

Ready

N33

Interface

Signal / Bus

FPGA Pin #

Channel 1

Data[0:31]

U25 T25 T28 T29 R33 R34 T30 T31 T33 T34 U26

U27 U33 U32 U28 V29 V32 V33 Y32 Y31 Y33 Y34

W29 Y29 W31 W32 Y28 Y27 W25 V25 W27 W26

Clock

V30

Write

W30

CE

W34

Ready

V34

Product Specification SMT166

Page 40 of 44

Last Edited: 17/06/2014 16:12:00