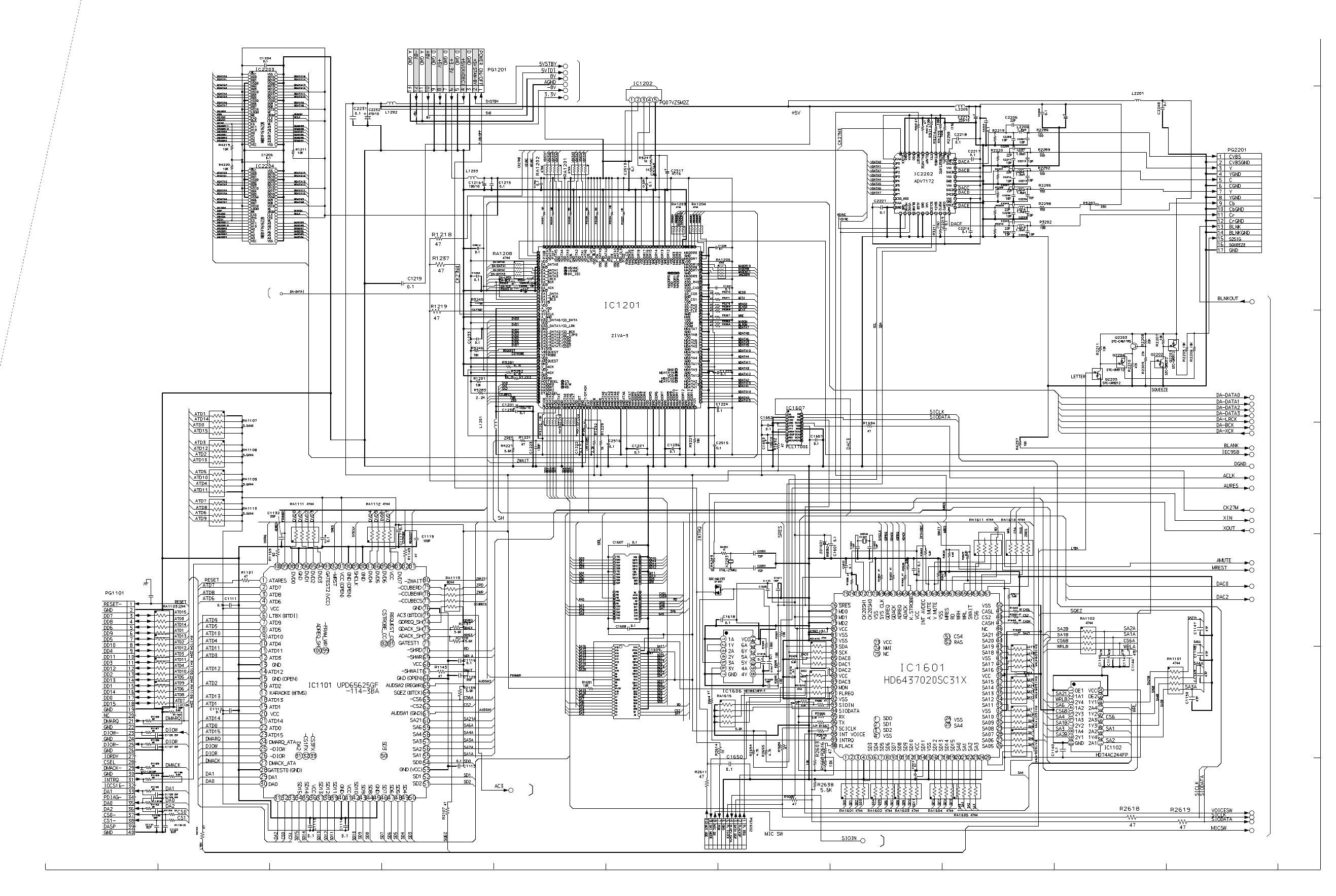

Deck-2 [dec] schematic diagram, Deck-2 [dec, Deck-2 – Hitachi DV-W1U User Manual

Page 28: Deck-2 dv-w1u, Sh1 m com, I/f ga mpeg decoder, 16mbit sdram, Pll inverter, Buffer

A

B

C

3

2

1

D

E

F

G

4

6

5

7

5 - 14

5 - 13

DECK-2

DECK-2

DECK-2 [DEC] SCHEMATIC DIAGRAM

9

10

11

12

8

5 - 15

DECK-2

DV-W1U

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

DECK-2 [DEC]

-8

0

F

-8

0

F

220u

220u

SW

SW

SW

SW

To

REGULATOR

[REG]

PG1901

1A

33A

2A

3A

4A

5A

6A

To

DECK-1

1A-6A

To

DECK-1

33A

220u

620

620

160

160

160

160

160

160

220u

220u

C2244

220/16

9A

10A

11A

12A

13A

14A

15A

16A

17A

18A

19A

32A

20A

21A

22A

23A

24A

25A

26A

27A

28A

29A

30A

31A

To

DECK-1

9A-32A

8A

To

DECK-1

8A

7A

To

DECK-1

7A

10

9

8

7

6

5

4

3

2

1

To

INTERFACE

[IF]

PG1905

IC1603

MSM5416258B-28J1

4Mbit DRAM

IC1602

MBM29F160TE-90

16Mbit FLASH ROM

16Mbit SDRAM

16Mbit SDRAM

C1100

0.1

To

DVD-ROM

PG1101

I/F GA

MPEG DECODER

2.5V REG.

VIDEO

ENCODER

PLL

INVERTER

SH1

m

COM

BUFFER

To

REAR JACK

[JAK]

PG1302