Functional description, Input processing, Scaler – Grass Valley 2090MDC User Manual

Page 26

20

2090MDC Instruction Manual

2090MDC HDTV Monitoring Downconverter

Functional Description

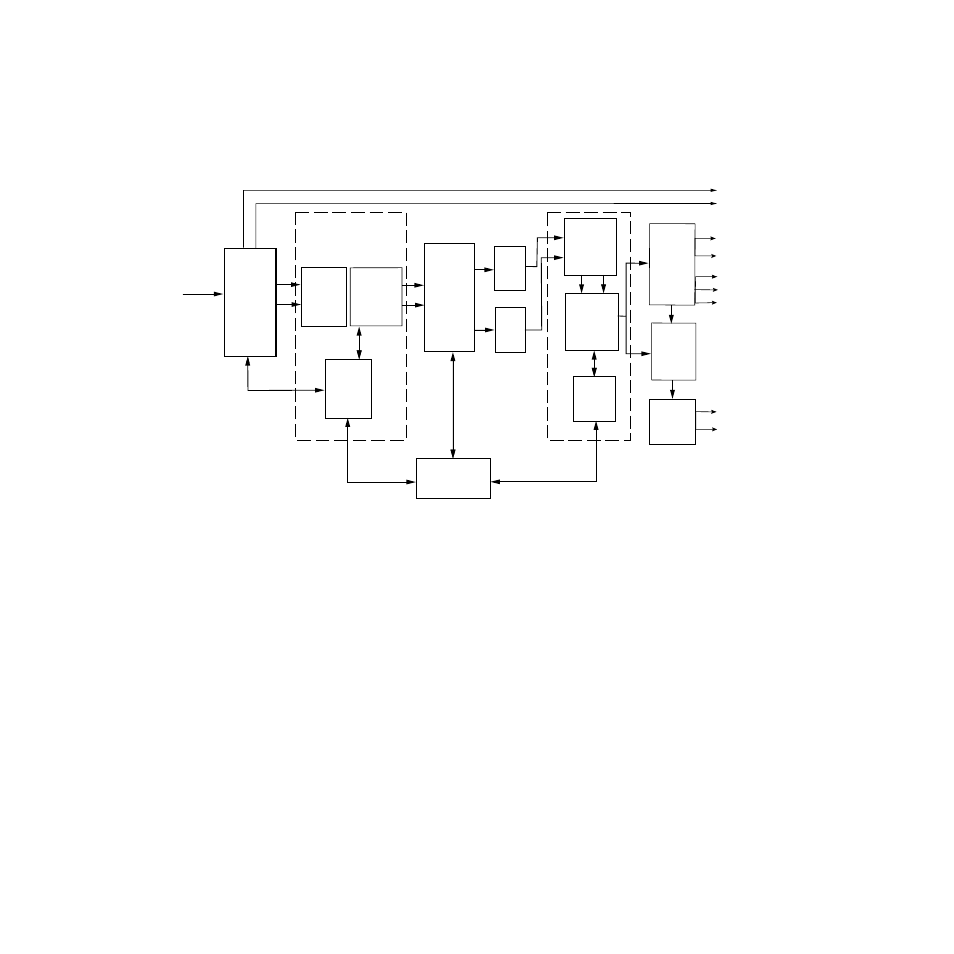

A block diagram of the 2090MDC is shown in

Figure 14. 2090MDC Block Diagram

Input Processing

The input section equalizes, re-clocks and de-serializes the HD input

signal.

One equalized and reclocked version of the input is fed back to the rear

looping BNC connector assembly through an output driver to become the

two HD outputs.

Scaler

The parallel video from the input processor is filtered and decimated in the

field/frame buffer in the HD FPGA and enters the scaling engine IC. Video

data from the Input Processing section is scaled down so that it will fit onto

a standard definition screen. The amount and type of scaling is pro-

grammed by the user; locally, by setting on-board switches, or remotely

through the frame controller.

SERIAL

HD in

HD

Out

NTSC/PAL

Out

SD

Out

8029_02

Microprocessor

Colorimetry

Converter

D1

Multiplexer

Scaling

Engine

NTSC

Encoder

&

RGB

Converter

D1

Serializer

&

Scrambler

SD

Driver

HD FPGA

SD FPGA

UV-

FIFO

Y-FIFO

Input

Timing

&

Control

SD

Timing

H

Halfband

Filters

Field/Frame

Buffers

Equalizer

&

Reclocker

Y

UV

Y

Y

UV

Y

UV

UV

R

G

B

Out