Dpram, Emif control registers, Dpram emif control registers – Sundance SMT363XC2 User Manual

Page 10

Version 2.2

Page 10 of 27

SMT363XC2 User Manual

DPRAM

The DPRAM in the FPGA is only intended to be used during this boot process; more

general use is not recommended.

A 128KB memory is directly connected to both the DSP and the NET+50 devices.

Each can access the memory independently and at their respective maximum data

rates.

The DPRAM is decoded as the boot ROM in the NET+50’s memory space.

The DPRAM supports the generation of interrupts to either of its ports. This

functionality is achieved by the DSP writing to a specific DPRAM address, which in

turn generates an interrupt to the NET+50 (PINT2* pin). Similarly, the NET+50 can

write to a specific address which generates an interrupt which can be routed to the

DSP.

EMIF Control Registers

The DSP has a single external memory interface (EMIF) which is 32 bits wide.

A full description of the registers used to control the EM

! Reference source not found.Error!

Reference source not found..

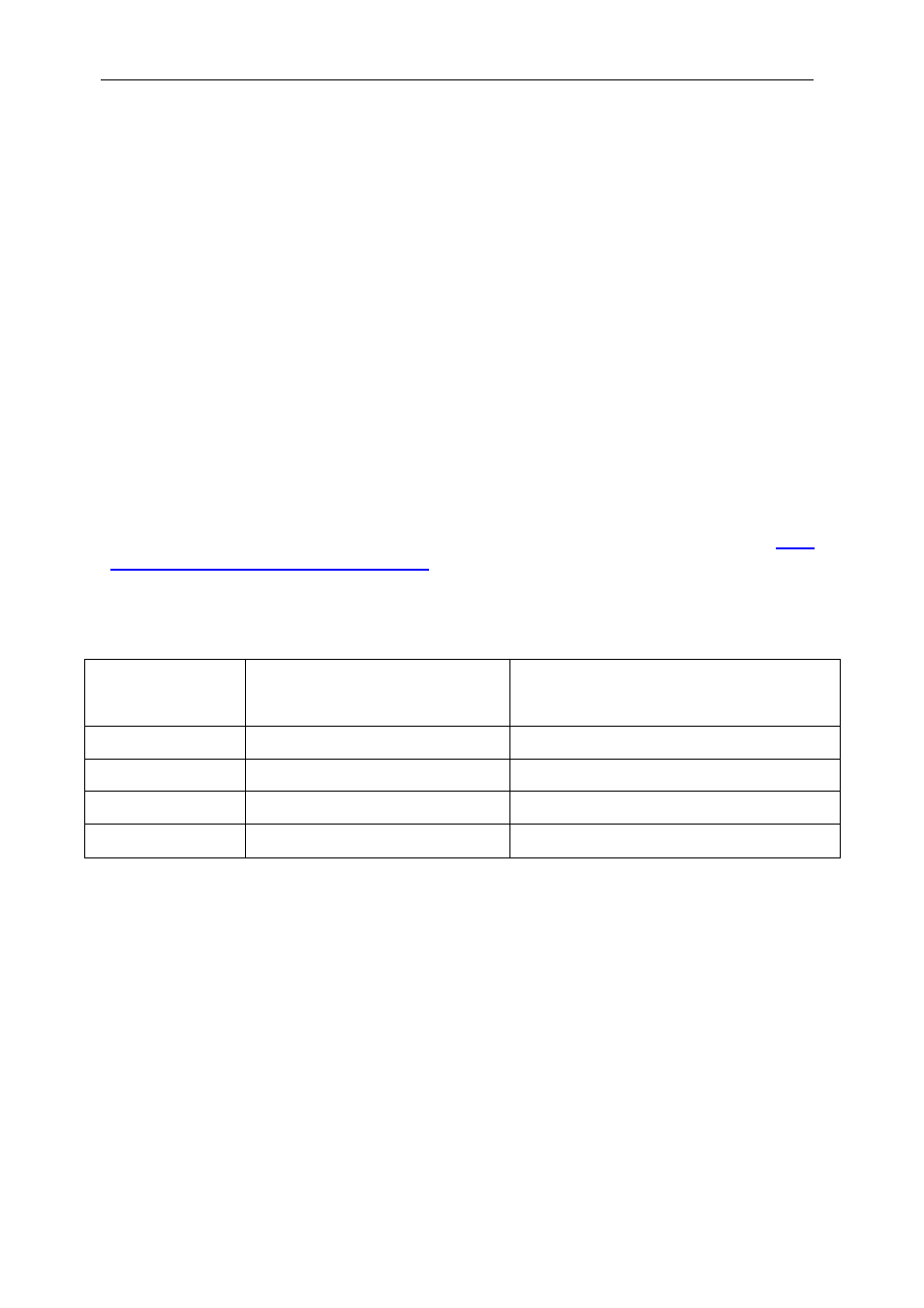

The standard bootstrap will initialise these registers to use the following resources:

Memory space

(EMIF)

Resource

Address range

CE0

SDRAM

0x80000000 - 0x83FFFFFF

CE1

Flash / IO Control

0x90000000 - 0x903FFFFF

CE2

DPRAM

0xA0000000 - 0xA7FFFFFF

CE3

Virtex

0xB0000000 - 0xB0FFFFFF

The power on (and reset) state for the semaphore enable (DPRAM related) is

disabled. This bit determines whether the flash or DPRAM-semaphore registers are

accessed on CE1.