Sundance SMT339 v.1.3 User Manual

Page 10

Version 1.2

Page 10 of 27

SMT339 User Manual V1.3

2.3.2 I

2

C Control

The DM642 DSP has a built-in I

2

C interface for controlling internal peripherals. This

2 wire serial bus is connected to 3 devices in the system. The devices and their

respective I

2

C addresses are illustrated in the table below.

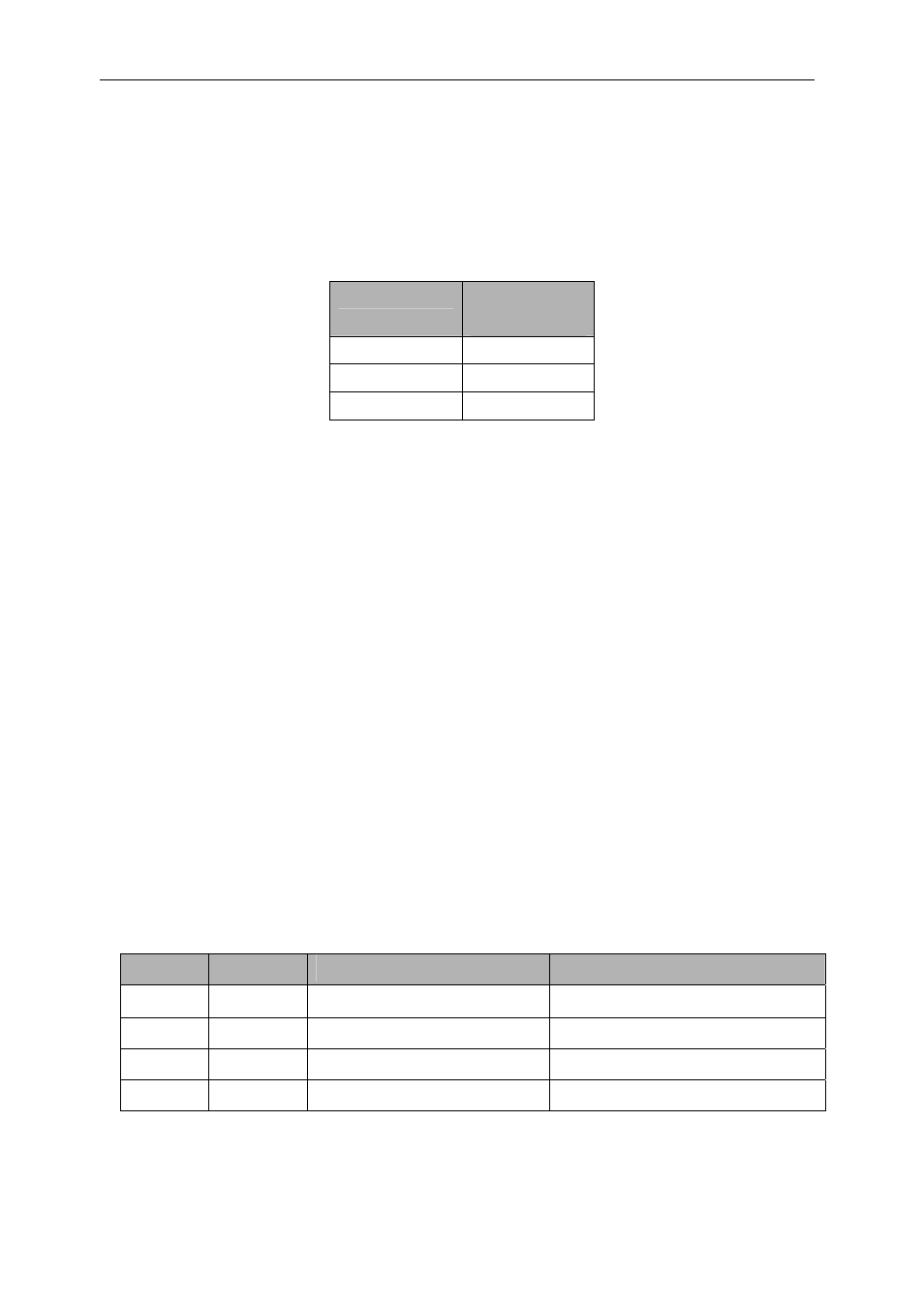

Device

Address

(LSB ‘0’- wr )

Video Decoder

0x40

Video Encoder

0x88

Virtex 4 **

NA

** No interface implemented in standard firmware.

2.4 Flash

8Mbytes of flash memory is provided with direct access by the DM642. This device

contains boot code for the DSP and the configuration data for the FPGA.

This is a 16-bit wide device.

The flash device can be re-programmed by the DM642 at any time. There is a

software protection mechanism to stop most errant applications from destroying the

device’s contents. For extra safety a jumper (JP1) must be inserted to allow write

operations.

Note that the flash memory is connected as a 16 bit device, but during a DM642 boot

(internal function of the C6x) only the bottom 8 bits are used.

There are a number of DSP General Purpose pins connected to the FLASH devices

Bank Pins in order to allow access to the upper FLASH areas. The Table below

shows the GPIO pins values and associated memory access areas.

GPIO10

GPIO9

DSP Memory Address

FLASH Access Address (16bit)

0

0

0x9000 0000 -> 0x900F FFFF

0x0000 0000 -> 0x000F FFFF

0

1

0x9000 0000 -> 0x900F FFFF

0x0010 0000 -> 0x001F FFFF

1

0

0x9000 0000 -> 0x900F FFFF

0x0020 0000 -> 0x002F FFFF

1

1

0x9000 0000 -> 0x900F FFFF

0x0030 0000 -> 0x003F FFFF