Sundance SMT148 User Manual

Page 29

Version 1.4

Page 29 of 35

SMT148 User Manual

ADC

The ADC interface is an input as well as an output node to the switch fabric. All eight

channels are controlled by this interface. It needs to receive settings before it can

transmit digitized samples to the interface it was initialized by.

To initialize a transfer or disconnect itself from the input node the ADC interface

expects to receive the following 32-bit word (4 consecutive bytes, LSB first):

Bit 31: new transfer initialization if 1.

Bit 30: disconnect from input node if 1, will result in a DONE pulse sent to the switch

fabric.

Bit 23 down to 16: output node address to which the digitized samples will be sent to

Bit 7 down to 0: Channels enable, 1 on bit X indicates that channel X will acquire

data, 0 that it will not.

After the ADC interface has been initialized it will start transmitting the digitized

samples through the switch fabric to the specified output node.

The first 32-bit word sent from the ADC interface to the switch fabric will address the

output node it needs to access.

Bit 31 down to 8: set to 0

Bit 7 down to 0: output node address (see table 14)

The next words sent to the switch fabric will have the following format:

Bit 31 down to 24: time stamp. This value is incremented by one every time a new

sample is available on a specific channel. If the receiver detects that 2 samples from

the same channel received consecutively have a time stamp difference not equal to

one, this means that some samples have been lost during transfer.

Bit 23 down to 16: channel to which the sample belongs, 1 on bit X indicates that the

sample belongs to channel X-16. All the other bits will be set to 0.

Bit 13 down to 0 : digitized sample value.

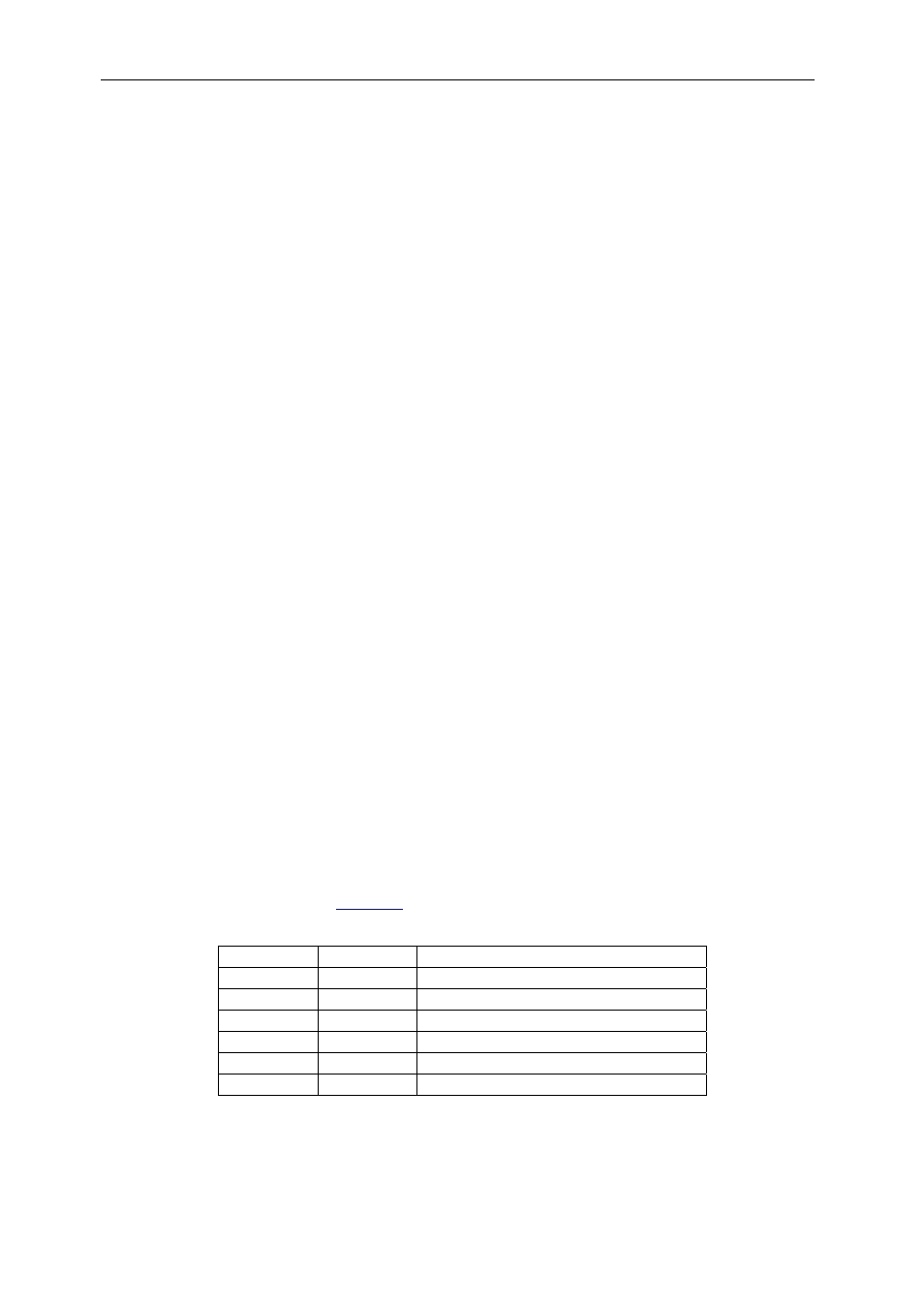

The ADC interface communicates with the ADC device on board using the following

nRD

Output

Read, active low

nCS

Output

Chip select, active low

nCONVST

Output

Convert start analog input, active low

CLKIN Output Conversion

Clock

BUSY

Input

Conversion is in progress

nSTBY

Output

Standby, active low

DATA_in

Input

14-bit data bus

Table 21 : ADC interface extra IO