Watchdog timers, Reset, Watchdog timers reset – Sundance SMT148 User Manual

Page 27

Version 1.4

Page 27 of 35

SMT148 User Manual

Watchdog timers

The watchdog timers are used for reset purposes by the different TIM modules in the

system. Each TIM can access its own watchdog timer and set a time that will elapse

before the TIM or all TIM modules are reset.

The watchdog timer expects 4 words (of one byte each). The first byte received is the

LSB; the fourth byte is the MSB. After receiving these four words the watchdog timer

will send a DONE pulse to the switch fabric in order for the input node to be

disconnected.

The four bytes received by the watchdog timer accounts for a 32-bit word:

Bit 29: All TIM reset if 1, only one TIM reset if 0.

Bit 28 down to 0: number of clock cycles before reset. If this number has been set to

0, the watchdog timer is disabled. The watchdog timer can be programmed for 1

clock cycle (10ns) up to 2^29-1 cycles (5.3s).

Each watchdog timer can be interrupted any time by writing 4 bytes of 0 to it.

On the switch fabric side the watchdog timer is compliant to interface to an output

node. The watchdog timer also interfaces to the reset circuitry with the following

signals.

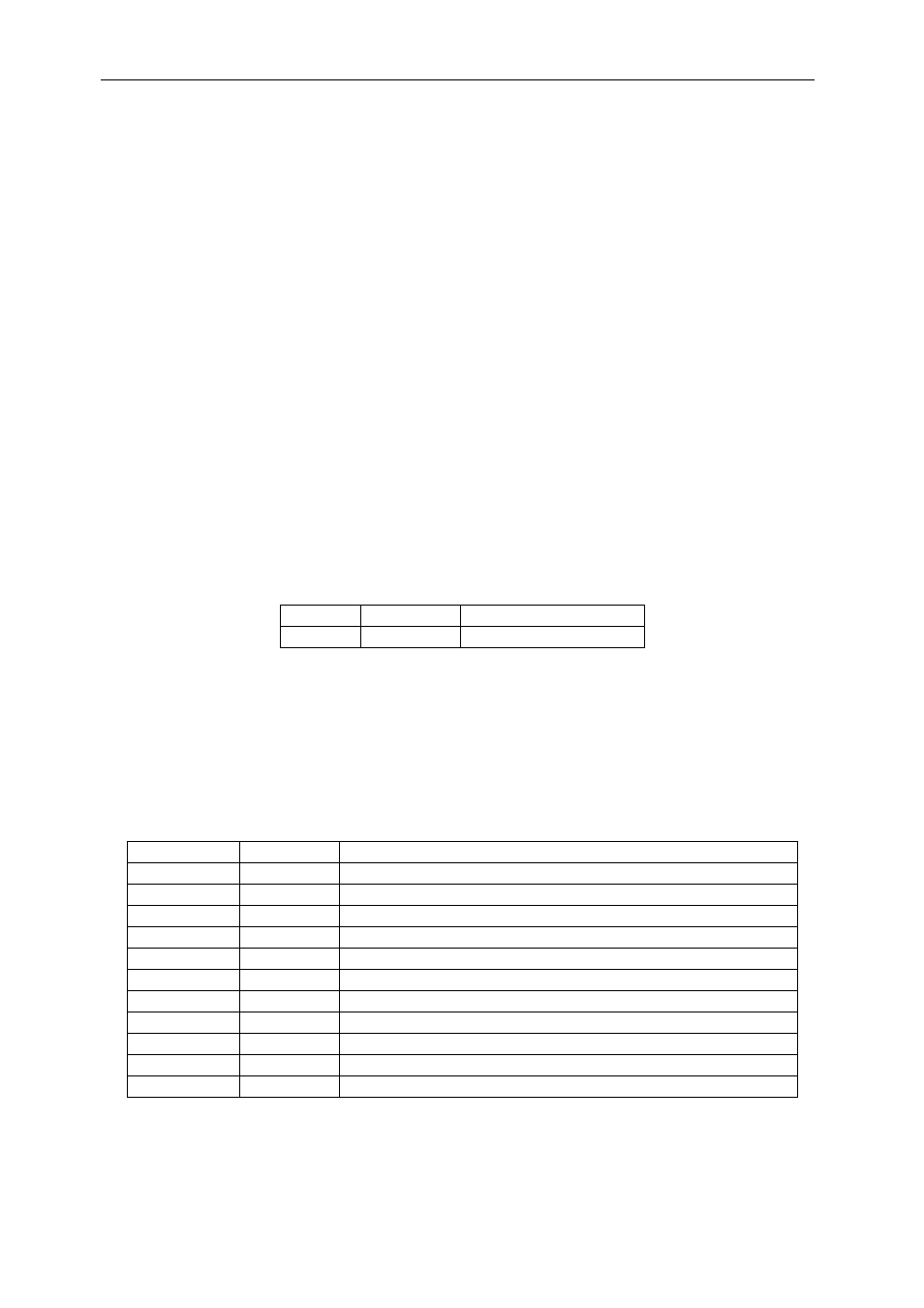

GRESET Output

Global reset to all TIM

TRESET Output

Reset one TIM only

Table 18 : Watchdog timer extra IO

Reset

The reset circuitry inside the FPGA is connected to the watchdog timers. When it

receives a GRESET pulse it will reset all TIM modules for 2^20 cycles (~10ms).

When it receives a TRESET pulse it will reset one TIM module for 2^20 cycles

(~10ms). The reset circuitry has the following inputs and outputs.

GRESET1

input

Global reset to all TIMs from watchdog timer 1

GRESET2

input

Global reset to all TIMs from watchdog timer 2

GRESET3

input

Global reset to all TIMs from watchdog timer 3

GRESET4

input

Global reset to all TIMs from watchdog timer 4

TRESET1

input

Reset TIM 1 from watchdog timer 1

TRESET2

input

Reset TIM 2 from watchdog timer 2

TRESET3

input

Reset TIM 3 from watchdog timer 3

TRESET4

input

Reset TIM 4 from watchdog timer 4

nTIM1RESET output

TIM1 reset, active low

nTIM2RESET output

TIM1 reset, active low

nTIM3RESET output

TIM1 reset, active low

nTIM4RESET output

TIM1 reset, active low

Table 19 : Reset IO