Diagnostic startup sequence – Sierra Video Yosemite User Manual

Page 79

504001 PROCESSOR

73

Diagnostic Startup Sequence

When the switcher is powered up or resets for any reason (as when a DIP Switch is changed), it

performs a series of self-tests, signaling progress using the DIP Array on the 504001 processor

board. The startup self-test sequence is fast but provides important diagnostic checks. The

sequence is as follows:

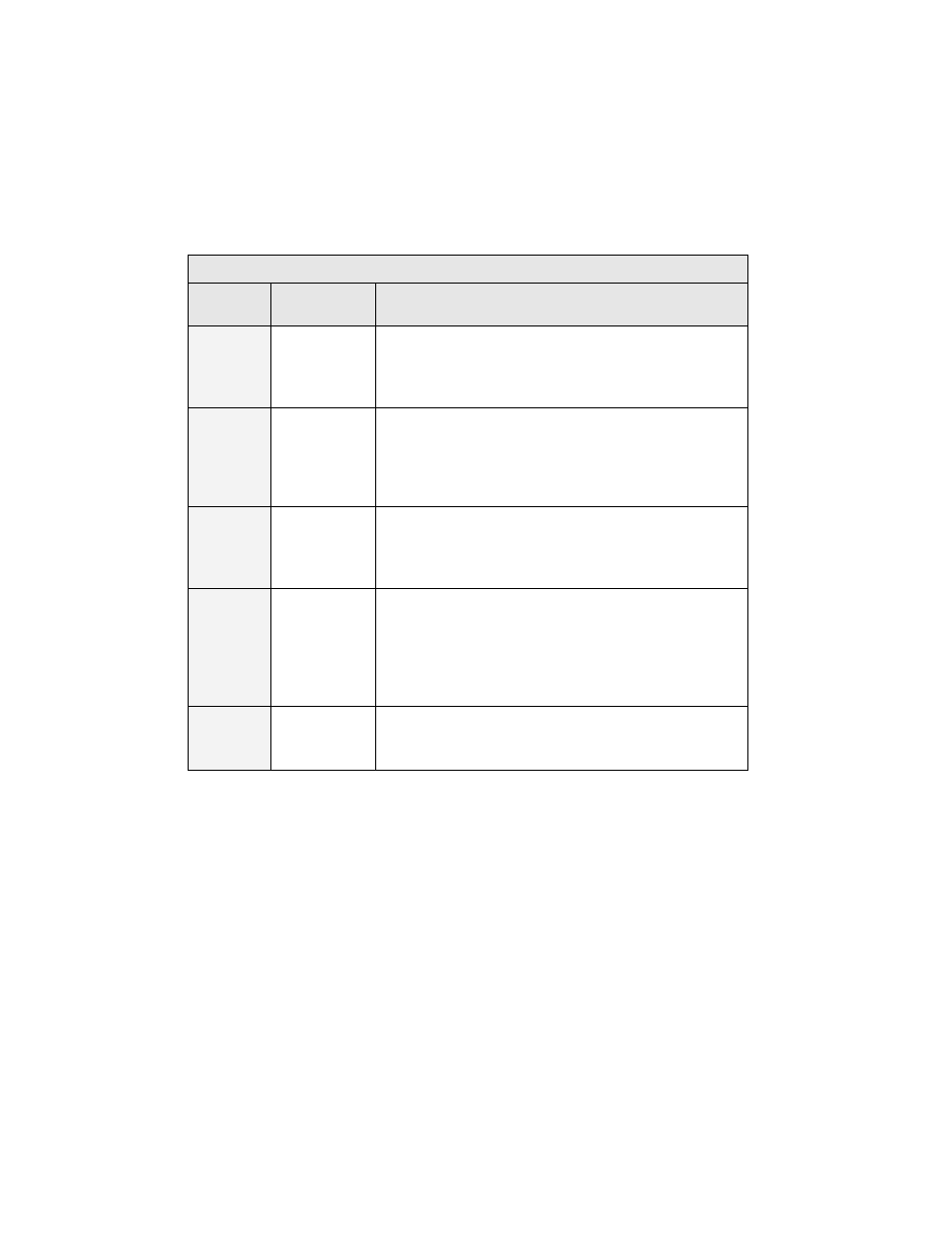

LED Startup Diganostics Sequence

Startup

Sequence

Initial LED

Combination

Operation

1

ALL LEDS Flash quickly for about one second, immediately after

startup (after initializing the processor registers). This

indicates that the processor is up and running an that the

LEDs all work.

2

LED1

Checksum of the EPROM is computed, and if not 0

(zero), LED #1 is flashed for about 3 seconds, then

normal operation begins. The makefile uses the cksmfile

utitlity to set the last EPROM byte so that the checksum

will be 0 (zero).

3

LED2

The external non-battery RAM is tested using a pseudo-

random number generator to generate random values. If

any location tests bad, LED #2 is flashed for about 3

seconds, then normal operation begins.

4

LED3

The external battery RAM is tested by complementing

each byte twice. If any location tests bad, LED #3 is

flashed for about 3 seconds, then normal operation

begins. The value of DIP0 is displayed on the LEDs for

one second, then the DIP1 values is displayed for one

second. This allows the DIP switches to be tested.

5

LED4

LED #4 is turned on, signaling system test has been

completed, and normal operation begins. LEDs should

begin normal cycling/counting operation.