Pci-das6402/16 block diagram, Pci-das6402/16 block diagram -2 – Measurement Computing PCI-DAS6402/16 User Manual

Page 8

PCI-DAS6402/16 User's Guide

Introducing the PCI-DAS6402/16

PCI-DAS6402/16 block diagram

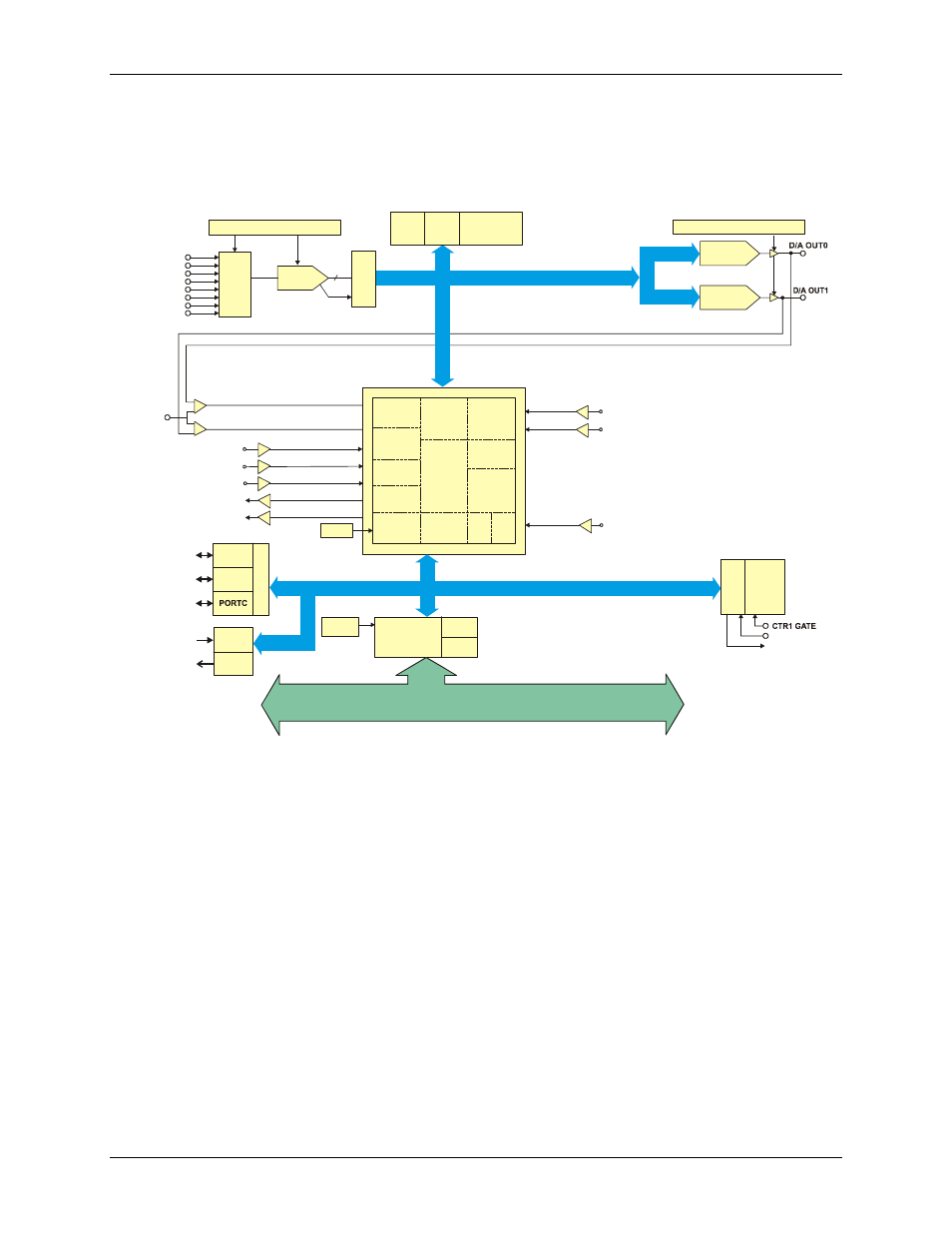

PCI-DAS6402/16 functions are illustrated in the block diagram shown here.

PORTA

PORTB

C

ont

ro

l

8

PCI BRIDGE

W/BUS MASTER

DMA

CH0

DMA

CH1

Boot

EEPROM

ADC

CNTL

STC

DAC

CNTL

Trigger

CNTL

ADC

Pacer

Decoder

IRQ

CNTL

TRIG_HI

ANALOG

TRIGGER

TRIG_LO

16-Bit

ADC

Mux

&

Gain

Analog In

64-ch s.e.

32-ch diff.

Gain and Offset Autocal

Co

nt

ro

l

DAC0

DAC1

Local BUS

PCI BUS (5V, 32-bit, 33 MHZ)

16

USER

CNTR

0

Sample

CNTL

Control/

Status

Regs

Memory

CNTL

QUEUE

CNTL

DAC

Pacer

DAC RT

CNTL

DMA

CNTL

Inputs

Outputs

24-bits DIO

40 MHz

D Q

EOC

16

Memory BUS

DAC 0/1

Buffer

(16K)

Queue

Buffer

(8K)

ADC

Buffer

(8K)

32K x 16

SRAM

HOLDING

REG

DIN(3:0)

DOUT(3:0)

200 kHz

16 Bit, 100KHz

16 Bit, 100KHz

16

EXTERNAL D/A TRIGGER/PACER GATE

D/A EXTERNAL PACER IN

INTERRUPT IN

CTR1 CLK

CTR1 OUT

A/D EXTERNAL PACER

A/D INTERNAL PACER OUT

SSH OUT

A/D PACER GATE

A/D START/STOP TRIGGER

Gain and Offset Autocal

FIRSTPORTA (7:0)

FIRSTPORTB(7:0)

FIRSTPORTC (7:0)

Figure 1-1. PCI-DAS6402/16 functional block diagram

1-2