Digital input/output, Interrupts, Digital input/output -6 – Measurement Computing PCI-DAS6402/16 User Manual

Page 27: Interrupts -6

PCI-DAS6402/16 User's Guide

Specifications

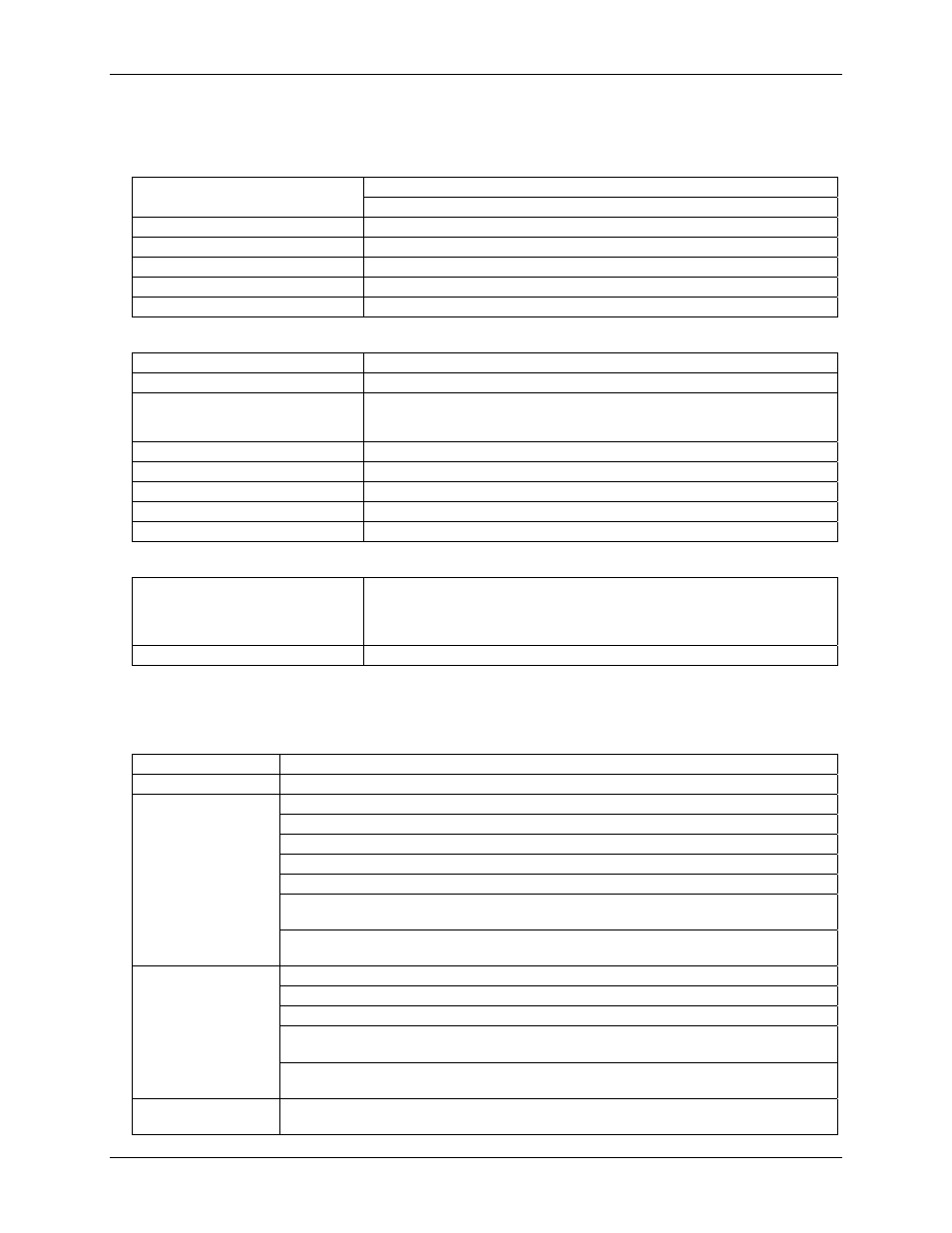

Digital input/output

Table 13. Digital input/output specifications (main connector)

Output: 74LS175

Digital type (main connector)

Input:

74LS244

Configuration

4 inputs, 4 outputs (DIN0 through DIN3; DOUT0 to DOUT3)

Output high voltage (IOH = -0.4 mA)

2.7 V min

Output low voltage (IOL = 8 mA)

0.5 V max

Input high voltage

2.0 V min, 7 volts absolute max

Input low voltage

0.8 V max, –0.5 volts absolute min

Table 14. Digital input/output specifications (DIO connector)

Digital type (digital I/O connector)

82C55

Number of I/O

24 (FIRSTPORTA Bit 0 through FIRSTPORTC Bit 7)

Configuration

!

2 banks of 8 and 2 banks of 4 or

!

3 banks of 8 or

!

2 banks of 8 with handshake

Input high voltage

2.0 V min, 5.5 V absolute max

Input low voltage

0.8 V max, –0.5 V absolute min

Output high voltage (IOH = -2.5 mA)

3.0 V min

Output low voltage (IOL = 2.5 mA)

0.4 V max

Power-up / reset state

Input mode (high impedance)

Table 15. Simultaneous sample and hold specifications

SSH output

TTL-compatible output, HOLD is asserted from start of the conversion for

Channel 0 through conversion of the last channel in the scan. Available at user

connector (SSH OUT / D/A PACER OUT). This pin is software selectable as

SSH OUT or D/A PACER OUT.

SSH polarity

HOLD high (default) or HOLD low, software selectable

Interrupts

Table 16. Interrupt specifications

Interrupts

PCI INTA# - mapped to IRQn via PCI BIOS at boot-time

Interrupt enable

Programmable through PLX9080

DAQ_ACTIVE:

Interrupt is generated when a DAQ sequence is active.

DAQ_STOP:

Interrupt is generated when A/D Stop Trigger In is detected.

DAQ_DONE:

Interrupt is generated when a DAQ sequence completes.

DAQ_FIFO_1/4_FULL:

Interrupt is generated when ADC FIFO is ¼ full.

DAQ_SINGLE:

Interrupt is generated after each conversion completes.

DAQ_EOSCAN:

Interrupt is generated after the last channel is converted in multi-

channel scans.

ADC interrupt sources

(sw programmable)

DAQ_EOSEQ:

Interrupt is generated after each interval delay during multi-

channel scans.

DAC_ACTIVE:

Interrupt is generated when DAC waveform circuitry is active.

DAC_DONE:

Interrupt is generated when a DAC sequence completes.

DAC_FIFO_1/4_EMPTY: Interrupt is generated DAC FIFO is ¼ empty.

DAC_HIGH_CHANNEL: Interrupt is generated when the DAC high channel output is

updated.

DAC interrupt sources

(sw programmable)

DAC_RETRANSMIT:

Interrupt is generated when the end of a waveform sequence has

occurred in retransmit mode.

External interrupt

Interrupt is generated via edge-sensitive transition on the External Interrupt pin. Rising/falling

edge polarity software selectable.

5-6