Appendix a: watchdog timer – NEXCOM NDiS 167 User Manual

Page 72

Copyright © 2012 NEXCOM International Co., Ltd. All Rights Reserved.

58

NDiS 167 User Manual

Appendix A: Watchdog Timer

Appendix A: Watchdog Timer

NDiS 167 features a watchdog timer that resets the CPU or generates an

interrupt if the processor stops operating for any reason. This feature ensures

system reliability in industrial standalone or unmanned environments.

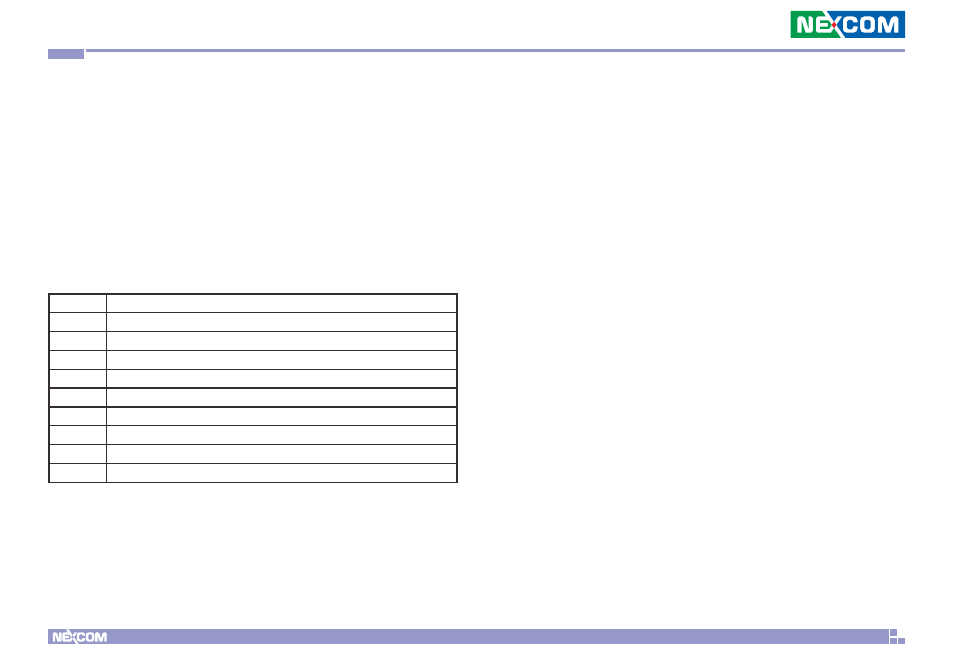

Watchdog Timer Control Register

(Index=71h, Default=00h)

Bit

Description

7

WDT is reset upon a CIR interrupt.

6

WDT is reset upon a KBC (mouse) interrupt.

5

WDT is reset upon a KBC (keyboard) interrupt.

4

WDT is reset upon a read or a write to the Game Port base address.

3-2

Reserved

1

Force Time-out. This bit is self-clearing.

WDT Status

0

1: WDT value reaches 0.

0: WDT value is not 0.

See also other documents in the category NEXCOM Hardware:

- EBC 352 (68 pages)

- EBC 353 (62 pages)

- EBC 355 (63 pages)

- EBC 354 (63 pages)

- ICES 268 (96 pages)

- ICES 667 (100 pages)

- ICES 254 (98 pages)

- NEX 604 (61 pages)

- NEX 608 (67 pages)

- ICES 668 (105 pages)

- NEX 607 (75 pages)

- NEX 609 (61 pages)

- NEX 611 (51 pages)

- NEX 613 (45 pages)

- NEX 617 (53 pages)

- NISE 101 (79 pages)

- NISE 104 (78 pages)

- NISE 2020 (84 pages)

- NISE 105A (78 pages)

- NISE 103 (83 pages)

- NISE 2110A (87 pages)

- NISE 2420 (84 pages)

- NISE 301 (74 pages)

- NISE 2310E (107 pages)

- NISE 2210E (110 pages)

- NISE 3100eP2 (75 pages)

- NISE 300 (95 pages)

- NISE 3140P2E (88 pages)

- NISE 3520P2E (125 pages)

- MAC 3500P2-GTS8 (120 pages)

- NISE 3600E (102 pages)

- NISE 3720P2E (85 pages)

- NISE 3640P2E (105 pages)

- NISE 3640M2E (108 pages)

- NISE 4000 (102 pages)

- nTUF 600 (100 pages)

- NEX 716VL2G (71 pages)

- NISE 4000P4E (128 pages)

- NISE 4000P2E (131 pages)

- NEX 732L2G (71 pages)

- NEX 883 (53 pages)

- NEX 890 (58 pages)

- NEX 980 (52 pages)

- NEX 852VL2 (62 pages)

- NEX 981 (47 pages)