Set constraints, Set constraints –5 – Altera 8B10B Encoder/Decoder MegaCore Function User Manual

Page 15

Chapter 2: Getting Started

2–5

8B10B Encoder /Decoder Walkthrough

May 2011

Altera Corporation

8B10B Encoder/Decoder MegaCore Function User Guide

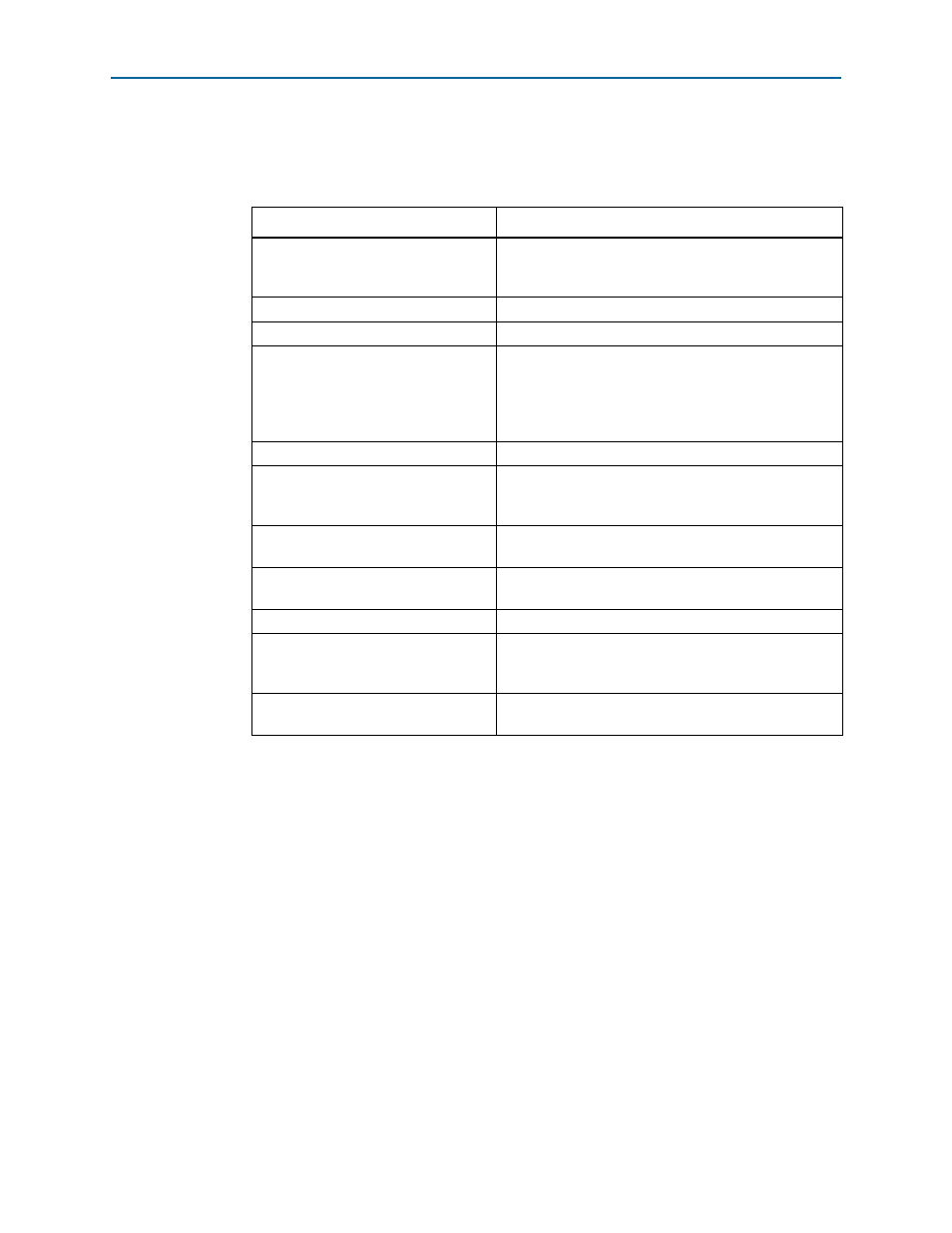

Table 2–1

describes the generated files and other files that may be in your project

directory. The names and types of files specified in the summary vary based on

whether you created your design with VHDL or Verilog HDL.

Set Constraints

The 8B10B Encoder/Decoder MegaCore function variations include a tool command

language (Tcl) script. Use this Tcl script to constrain your design.

To run the Tcl script in the Quartus II software, in a Win32 operating system, follow

either of these sets of steps:

1. Select TCL Scripts (Tools menu).

2. Select the applicable Tcl file for your variation:

<variation name>_constraints. tcl

3. Click Run.

or

Table 2–1. Generated Files

(Note 1)

Filename

(2)

Description

<variation name>.bsf

Quartus II symbol file for the MegaCore function

variation. You can use this file in the Quartus II block

diagram editor.

<

variation name

>.

cmp

VHDL component declaration file

<variation name>.html

The MegaCore function report file.

<variation name>.v

A MegaCore function variation file, which defines a

Verilog HDL top-level description of the custom

MegaCore function. Instantiate the entity defined by this

file inside of your design. Include this file when compiling

your design in the Quartus II software.

<

variation name

>

.vo

Verilog HDL IP functional simulation model.

<variation name>_bb.v

Verilog HDL black-box file for the MegaCore function

variation. Use this file when using a third-party EDA tool

to synthesize your design.

<

variation name

>_

constraints.tcl

Tool command language (tcl) script used to set

constraints.

<

variation name

>_

enc8b10b.ocp

An OpenCore Plus file, needed for time-limited or tethered

hardware evaluation.

<

variation name

>_

enc8b10b.v

Verilog HDL RTL for this MegaCore function variation.

<

variation name

>

_run_modelsim.tcl

A Tcl script to automate the process of running the

provided demo testbench with the IP functional

simulation model.

<

variation name

>

_tb.v

A Verilog HDL module with the top-level demo testbench

for the core.

Notes to

Table 2–1

:

(1) These files are variation dependent, some may be absent or their names may change.

(2) <variation name> is a prefix variation name supplied automatically by the MegaWizard interface.

(3) If you choose the decoder mode, the file name is