User ’s manual epi-qm67 user ’s manual 43 – Avalue EPI-QM67 User Manual

Page 43

User

’s Manual

EPI-QM67 User

’s Manual 43

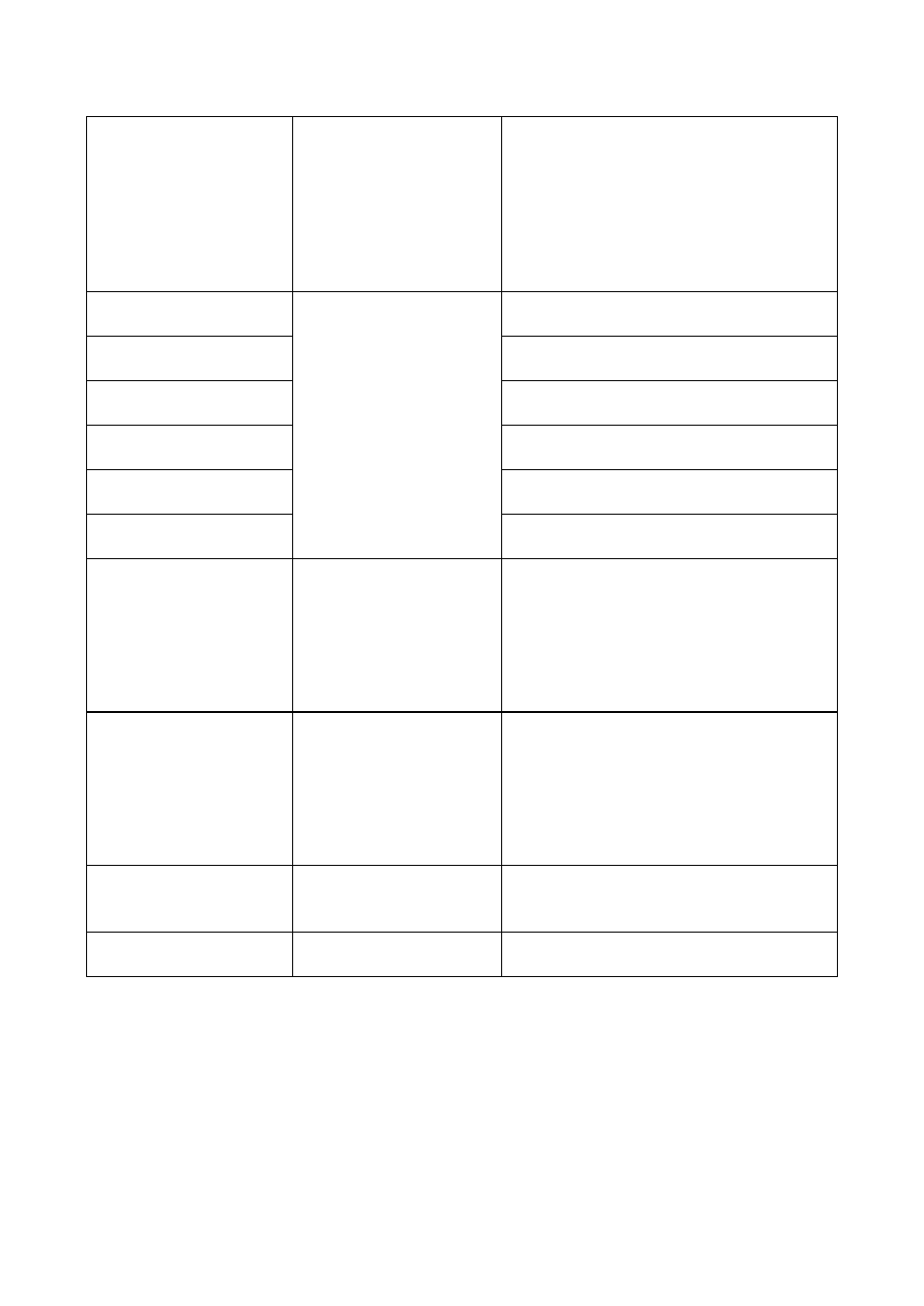

PCI Latency Timer

32 PCI Bus Clocks,

64 PCI Bus Clocks,

96 PCI Bus Clocks,

128 PCI Bus Clocks,

160 PCI Bus Clocks,

192 PCI Bus Clocks,

224 PCI Bus Clocks,

248 PCI Bus Clocks

Value to be programmed into PCI Latency

Register.

VGA Palette Snoop

Enabled,

Disabled

Enable or Disable VGA Palette Registers

Snooping.

PERR# Generation

If ENABLED allows generation of Extended

Synchronization patterns.

SERR# Generation

Enables or Disables PCI Devices to Generate

SERR#.

Relaxed Ordering

Enables or Disables PCI Express Device

Relaxed Ordering.

Extended Tag

If ENABLED allows Devices to use 8-bit Tag

field as a requester.

No Snoop

Enables or Disables PCI Express Devices No

Snoop option.

Maximum Payload

Auto

128 Bytes,

256 Bytes,

512 Bytes,

1024 Bytes,

2048 Bytes,

4096 Bytes

Set Maximum Payload of PCI Express Device

or allow System BIOS to select the value.

Maximum Read Request

Auto

128 Bytes,

256 Bytes,

512 Bytes,

1024 Bytes,

2048 Bytes,

4096 Bytes

Set Maximum Read Request Size of PCI

Express Device or allow System BIOS to

select the value.

ASPM Support

Disable,

Auto,

Force L0

Set the ASPM Level: Force L0

– Force all links

to L0 State: Auto

– BIOS auto configure:

DISABLE

– Disables ASPM

Extended Synch

Enable,

Disable

If ENABLED allows generation of Extended

Synchronization patterns.