Nb pci-e port – ADLINK Express-BE User Manual

Page 59

Express-BE

Page 59

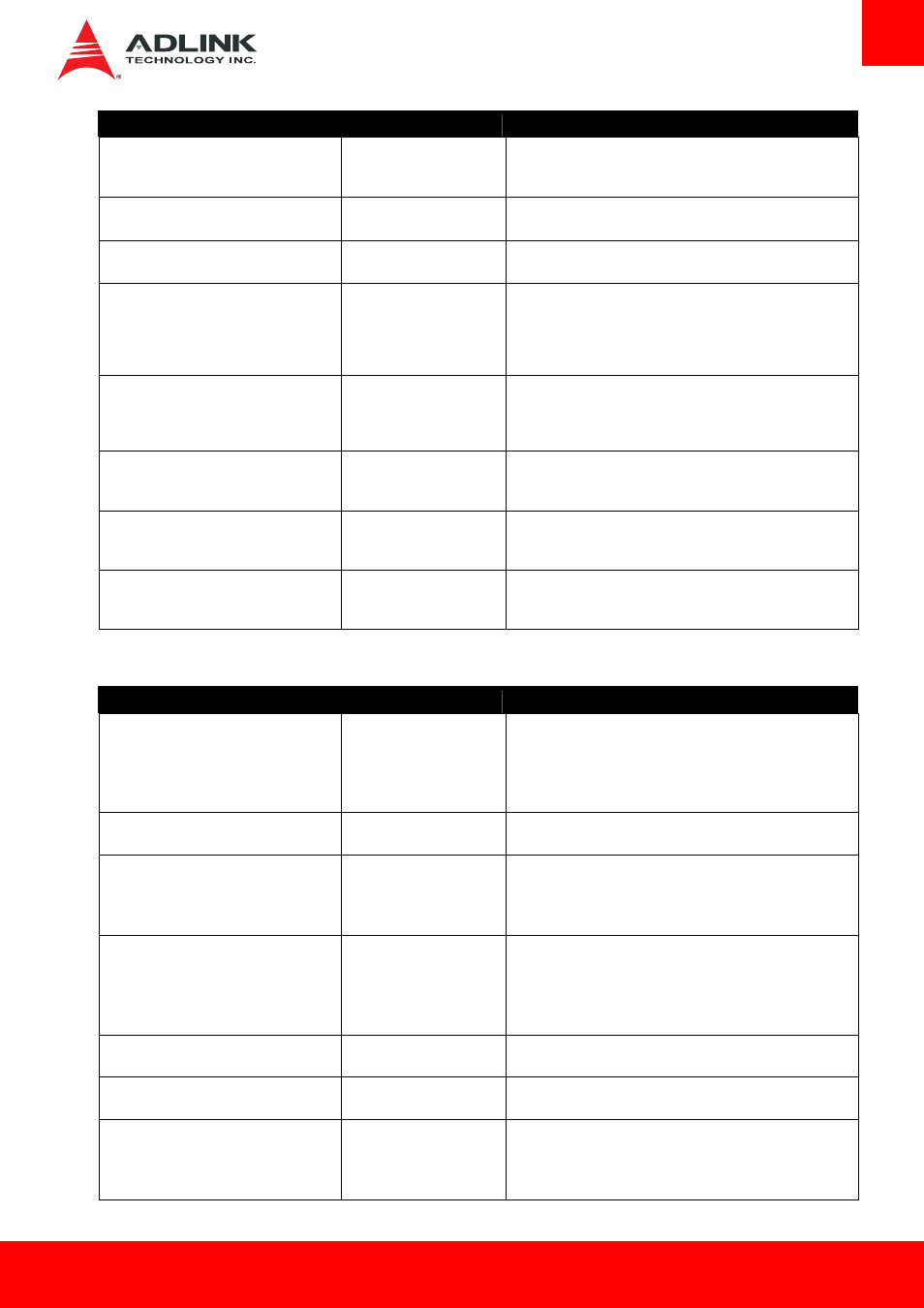

Feature

Options

Description

IDO Completion Enable

Enabled

Disabled

If supported by hardware and set to "Enabled", this permits setting

the number of ID-Based Ordering (IDO) bit (Attribute[2]) requests

to be initiated.

LTR Mechanism Enable

Enabled

Disabled

If supported by hardware and set to "Enabled", this enables the

Latency Tolerance Reporting (LTR) Mechanism.

End-End TLP Prefix Blocking

Enabled

Disabled

If supported by hardware and set to "Enabled", this function will

block forwarding of TLPs containing End-End TLP Prefixes.

Target Link Speed

Auto

Force to 2.5 GT/s

Force to 5.0 GT/s

If supported by hardware and set to "Force to 2.5 GT/s" for

Downstream Ports, this sets an upper limit on Link operational

speed by restricting the values advertised by the Upstream

component in its training sequences. When "Auto" is selected HW

initialized data will be used.

Clock Power Management

Enabled

Disabled

If supported by hardware and set to "Enabled", the device is

permitted to use CLKREQ# signal for power management of Link

clock in accordance to protocol defined in appropriate form factor

specification.

Compliance SOS

Enabled

Disabled

If supported by hardware and set to "Enabled", this will force

LTSSM to send SKP Ordered Sets between sequences when

sending Compliance Pattern or Modified Compliance Pattern.

Hardware Autonomous Width

Enabled

Disabled

If supported by hardware and set to "Disabled", this will disable the

hardware"s ability to change link width except width size reduction

for the purpose of correcting unstable link operation.

Hardware Autonomous Speed

Enabled

Disabled

If supported by hardware and set to "Disabled", this will disable the

hardware"s ability to change link speed except speed rate

reduction for the purpose of correcting unstable link operation.

7.3.7.3.

NB PCI-E Port

Feature

Options

Description

NB GPP Core Config

GPP_CORE_x4

GPP_CORE_x2x2

GPP_CORE_x2x1x1

GPP_CORE_x1x1x2

GPP_CORE_x1x1x1x1

NB GPP Core Configuration

Dev2 Fun1 (Lamar J119)

Enabled

Disabled

Dev2 Fun1 GFX Slot (Lamar J119) Enabled/Disabled

ASPM Mode Control

Disabled

L0s Entry

L1 Entry

L0s And L1 Entry

NB Root Port ASPM Mode Control

Hotplug Mode Control

Disabled

Hotplug Basic

Hotplug Server

Hotplug Enhanced

Hotplug Inboard

NB Root Port Hotplug Mode Control

Dev2 Fun2 (J3601)

Enabled

Disabled

Dev2 Fun2 GFX Slot (J3601) Enabled/Disabled

Dev3 Fun1

Enabled

Disabled

Dev3 Fun1 Enabled/Disabled

ASPM Mode Control

Disabled

L0s Entry

L1 Entry

L0s And L1 Entry

NB Root Port ASPM Mode Control