Table 1-5: pxes-2780 reference clock priority, Preliminary – ADLINK PXES-2780 User Manual

Page 28

18

Introduction

chronization. The independent buffers drive the clock signal to

each peripheral slot.

These common reference clock signals can synchronize multi-

ple modules in a PXI Express chassis. PXI modules with

phase-lock loop circuits can lock reference clocks to generate

an in-phase timebase.

The PXI_CLK10 and PXIe_CLK100 clocks are in-phase

according to the PXI-5 specification. Since the external 10MHz

clock input can override the onboard 10MHz clock source,

a phase-lock loop (PLL) circuit on the backplane synchro-

nizes the PXIe_CLK100 and external 10MHz clock.

The PXES-2780 PXI chassis automatically selects the 10 MHz

reference clock source from among:

Z

Built-in accurate 10 MHz clock source

Z

External 10 MHz clock through a BNC connector

Z

PXI_CLK10_IN pin on the system timing slot

Priority of the 10MHz reference clock is as follows.

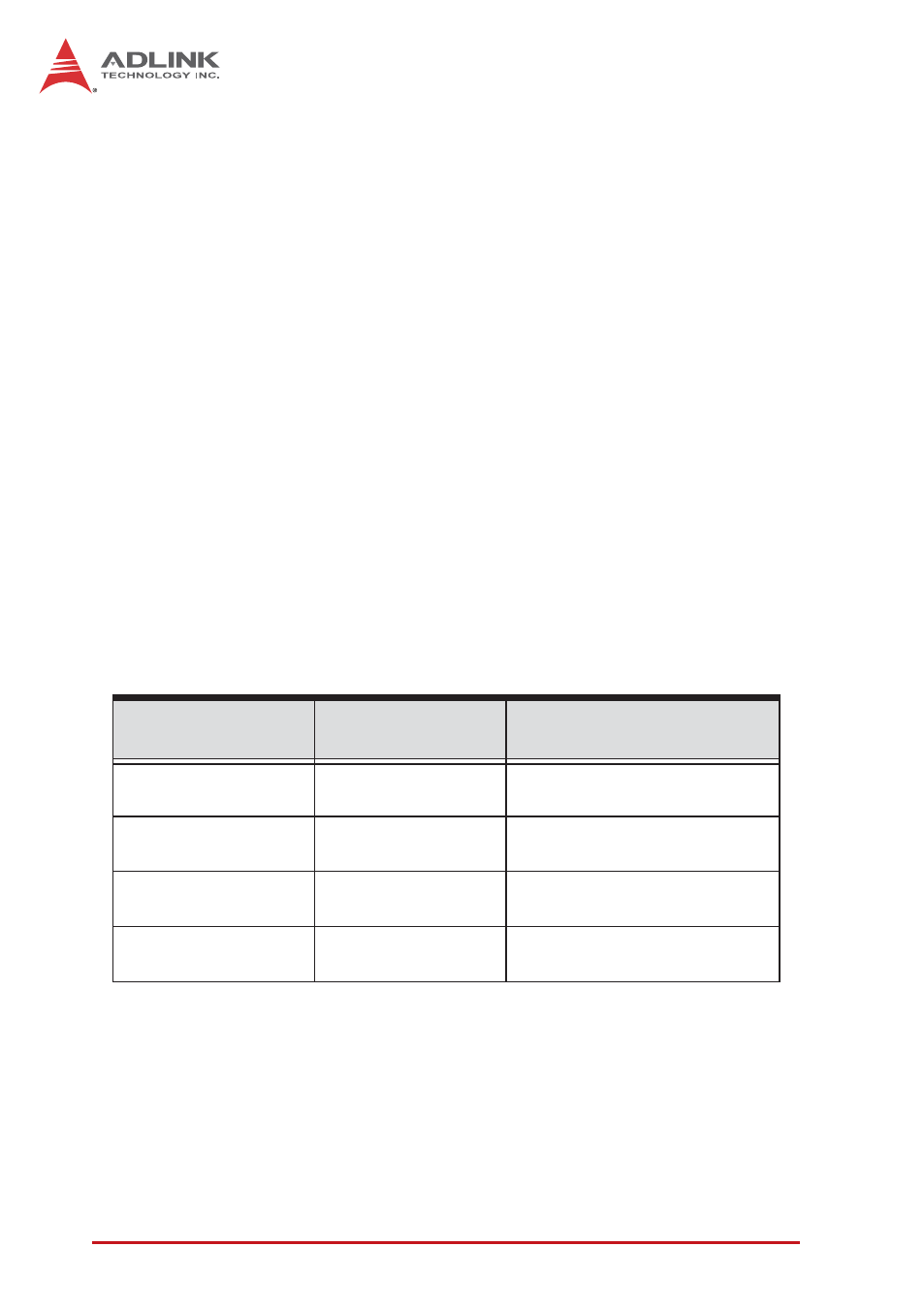

Table 1-5: PXES-2780 Reference Clock Priority

System Timing Slot

(5th slot)

BNC Connector on

Rear Panel

10mhz Clock Driven to

Peripheral Slots

No clock present

No clock present

10MHz clock is generated by

backplane

No clock present

10MHz clock

present

Clock from BNC connector is

driven to all peripheral slots

10MHz clock present No clock present

Clock from system timing slot

is driven to all peripheral slots

10MHz clock present 10MHz clock

present

Clock from system timing slot

is driven to all peripheral slots

PRELIMINARY