Operation theorem • 23, Figure 4.1.3 delay trigger – ADLINK PXI-2502 User Manual

Page 31

Operation Theorem

• 23

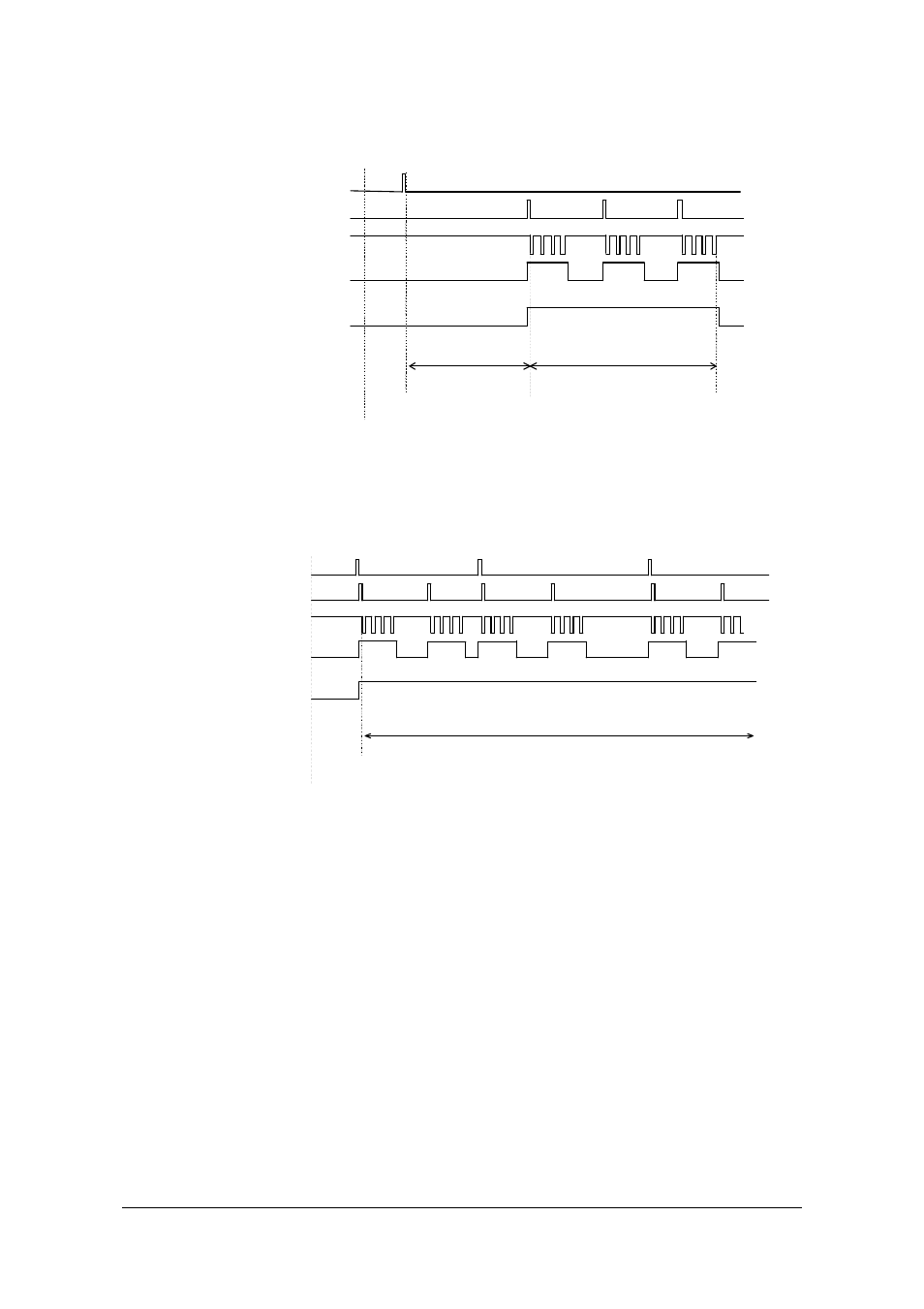

(NumChan _Counter=4, PSC_Counter=3)

Acquisition_in_progress

Scan_start

AD_conversion

Scan_in_progress

Acquired & stored data

(3 scans)

Operation start

Trigger

Delay until

Delay_Counter

reaches 0

Figure 4.1.3 Delay trigger

(NumChan _Counter=4, SC_Counter=2, retrig_no=3)

Acquisition_in_progress

Scan_start

AD_conversion

Scan_in_progress

Acquired & stored data

(6 scans)

Operation start

Trigger

Figure 4.1.4 Post trigger with retrigger

4.1.4.4 Bus-mastering DMA Data Transfer

Bus Mastering DMA Mode

In order to utilize the maximum PCI bandwidth, PCI bus-mastering DMA is

used for high speed DAQ boards. The bus-mastering capability of the PLX

PCI controller, takes over the PCI bus when it becomes the master. Bus

mastering reduces the required size of on-board memory as well as CPU

loading since data is directly transferred to the host PC’s memory without

CPU intervention.