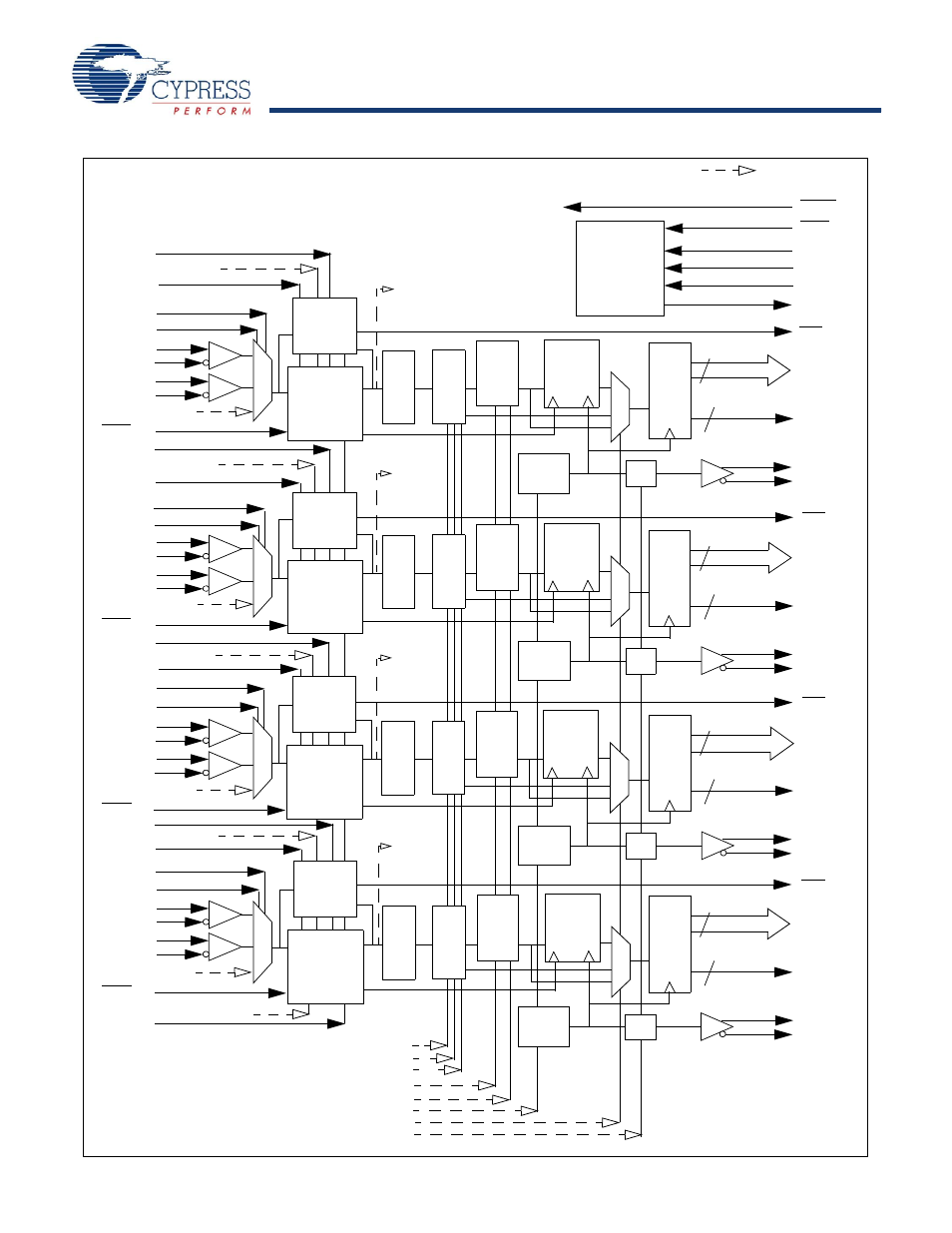

Receive path block diagram, Receive path block, Jtag boundary scan controller – Cypress CYV15G0404DXB User Manual

Page 4

CYV15G0404DXB

Document #: 38-02097 Rev. *B

Page 4 of 44

INA1+

INA1–

INA2+

INA2–

INSELA

INB1+

INB1–

INB2+

INB2–

INSELB

INC1+

INC1–

INC2+

INC2–

INSELC

IND1+

IND1–

IND2+

IND2–

INSELD

Clock &

Data

Recovery

PLL

Shif

ter

Clock &

Data

Recovery

PLL

Shif

ter

Clock &

Data

Recovery

PLL

Shif

ter

Clock &

Data

Recovery

PLL

Shif

ter

LFID

LFIC

LFIB

LFIA

8

RXSTC[2:0]

RXDC[7:0]

3

8

RXSTB[2:0]

RXDB[7:0]

3

8

RXSTD[2:0]

RXDD[7:0]

3

8

RXSTA[2:0]

RXDA[7:0]

3

Receive

Signal

Monitor

Receive

Signal

Monitor

Receive

Signal

Monitor

Receive

Signal

Monitor

Out

p

u

t

Regi

ster

Output

Re

gister

Output

Re

gister

Out

p

ut

Reg

ister

Elasticity

Buf

fer

Framer

RXCLKD+

RXCLKD–

10B/8B

BIS

T

El

asti

city

Buf

fer

10B/8B

BIST

F

ram

er

Elasticity

Buf

fer

10B/8B

BIS

T

F

ramer

Ela

s

ti

ci

ty

Buf

fer

10

B/8

B

BIST

Framer

÷2

RXCLKC+

RXCLKC–

÷2

RXCLKB+

RXCLKB–

÷2

RXCLKA+

RXCLKA–

÷2

RXRATE[A..D]

FRAMCHAR[A..D]

RFEN[A..D]

JTAG

Boundary

Scan

Controller

TDO

TMS

TCLK

TDI

Clock

Select

Clock

Select

Clock

Select

Clock

Select

RXCKSEL[A..D]

RESET

Receive Path Block

=

Internal Signal

RXPLLPDA

RFMODE[A..D][1:0]

LPENA

RXBIST[A..D]

DECMODE[A..D]

LPENB

LPENC

LPEND

TRST

RXPLLPDB

RXPLLPDC

RCLKEND

RXPLLPDD

DECBYP[A..D]

SPDSELA

SPDSELB

SPDSELC

SPDSELD

ULCB

ULCA

ULCC

ULCD

LDTDEN

TXLBD

TXLBC

TXLBB

TXLBA

RECLCK[A..D] are Internal Reclocker Signals

SDASEL[A..D][1:0]

RCLKENC

RCLKENB

RCLKENA

RECLCKD

RECLCKC

RECLCKB

RECLCKA

TXLB[A..D] are Internal Serial Loopback Signals