Cypress CYV15G0404DXB User Manual

Page 29

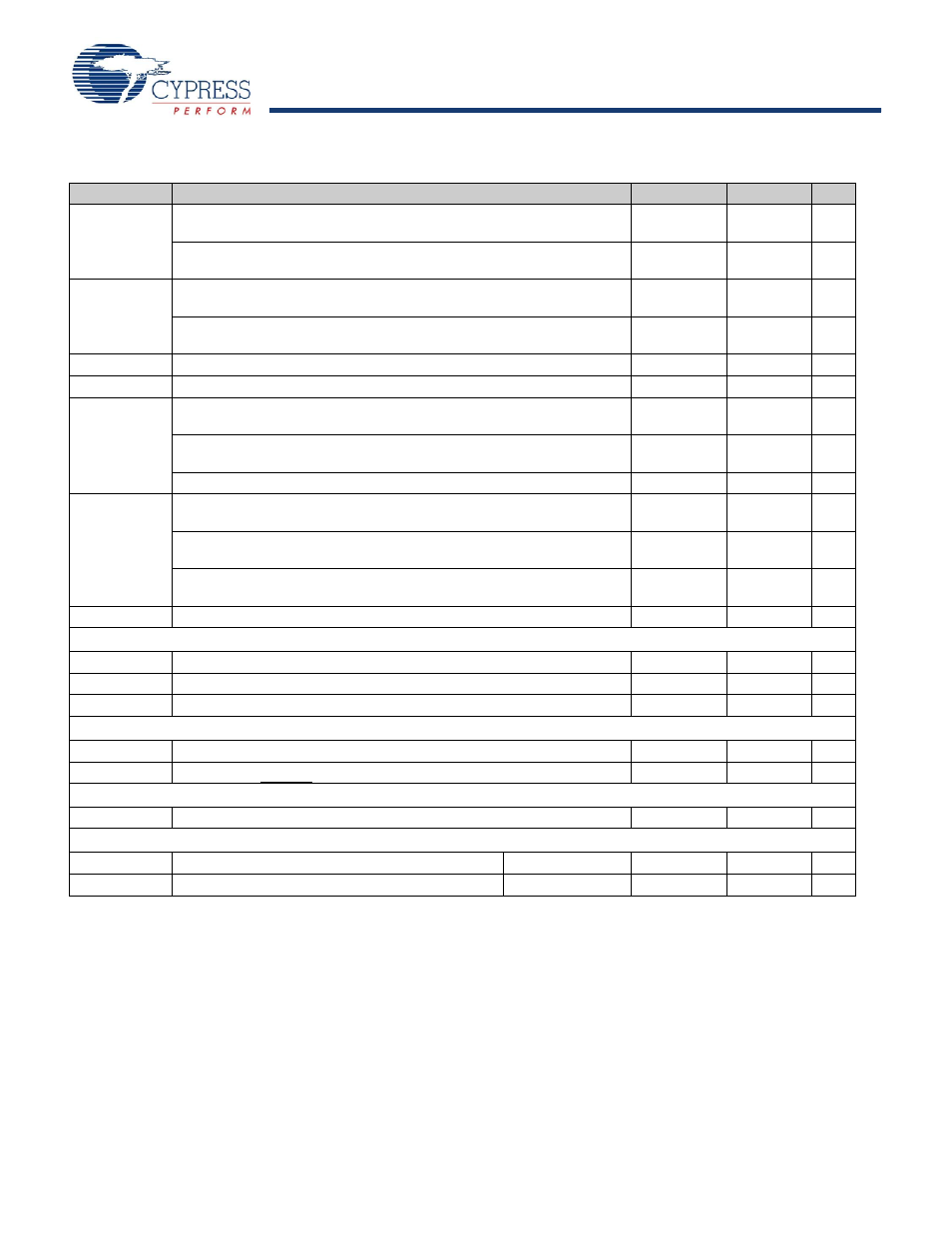

CYV15G0404DXB

Document #: 38-02097 Rev. *B

Page 29 of 44

t

TREFDS

Transmit Data Set-up Time to

REFCLKx - Full Rate

(TXRATEx = 0, TXCKSELx

= 1)

2.4

ns

Transmit Data Set-up Time to

REFCLKx - Half Rate

(TXRATEx = 1, TXCKSELx

= 1)

2.3

ns

t

TREFDH

Transmit Data Hold Time from REFCLKx - Full Rate

(TXRATEx = 0, TXCKSELx

= 1)

1.0

ns

Transmit Data Hold Time from REFCLKx - Half Rate

(TXRATEx = 1, TXCKSELx

= 1)

1.6

ns

t

RREFDA

Receive Data Access Time to

REFCLKx (RXCKSELx = 1)

9.7

ns

t

RREFDW

Receive Data Valid Time Window (RXCKSELx

= 1)

10UI – 5.8

ns

t

REFxDV–

Received Data Valid Time to RXCLK when RXCKSELx

= 1

(TXRATEx = 0, RXRATEx = 0)

10UI

– 6.16

ns

Received Data Valid Time to RXCLK when RXCKSELx

= 1

(TXRATEx = 0, RXRATEx = 1)

5UI – 2.53

ns

Received Data Valid Time to RXCLK when RXCKSELx

= 1 (TXRATEx = 1) 10UI – 5.86

ns

t

REFxDV+

Received Data Valid Time from RXCLK when RXCKSELx

= 1

(TXRATEx = 0, RXRATEx = 0)

1.4

ns

Received Data Valid Time from RXCLK when RXCKSELx

= 1

(TXRATEx = 0, RXRATEx = 1)

5UI – 1.83

ns

Received Data Valid Time from RXCLK when RXCKSELx

= 1

(TXRATEx = 1)

1.0

ns

t

REFRX

REFCLKx Frequency Referenced to Received Clock Period

–0.15

+0.15

%

CYV15G0404DXB Bus Configuration Write Timing Characteristics

Over the Operating Range

t

DATAH

Bus Configuration Data Hold

0

ns

t

DATAS

Bus Configuration Data Setup

10

ns

t

WRENP

Bus Configuration WREN Pulse Width

10

ns

CYV15G0404DXB JTAG Test Clock Characteristics

Over the Operating Range

f

TCLK

JTAG Test Clock Frequency

20

MHz

t

TCLK

JTAG Test Clock Period

50

ns

CYV15G0404DXB Device RESET Characteristics

Over the Operating Range

t

RST

Device RESET Pulse Width

30

ns

CYV15G0404DXB Transmit Serial Outputs and TX PLL Characteristics Over the Operating Range

Parameter

Description

Condition

Min.

Max.

Unit

t

B

Bit Time

5128

666

ps

Notes

26. Since this timing parameter is greater than the minimum time period of REFCLK it sets an upper limit to the frequency in which REFCLKx can be used to clock

the receive data out of the output register. For predictable timing, users can use this parameter only if REFCLK period is greater than sum of t

RREFDA

and set-up

time of the upstream device. When this condition is not true, RXCLKx± (a buffered or divided version of REFCLK when RXCKSELx = 1) could be used to clock

the receive data out of the device.

27. Measured using a 50% duty cycle reference clock

28. REFCLKx± has no phase or frequency relationship with the recovered clock(s) and only acts as a centering reference to reduce clock synchronization time.

REFCLKx± must be within

±1500 PPM (±0.15%) of the transmitter PLL reference (REFCLKx±) frequency. Although transmitting to a HOTLink II receiver neces-

sitates the frequency difference between the transmitter and receiver reference clocks to be within ±1500-PPM, the stability of the crystal needs to be within the

limits specified by the appropriate standard when transmitting to a remote receiver that is compliant to that standard. For example, to be IEEE 802.3z Gigabit

Ethernet compliant, the frequency stability of the crystal needs to be within ±100 PPM.l.

29. While sending continuous K28.5s, outputs loaded to a balanced 100

Ω load, measured at the cross point of differential outputs, over the operating range.

30. While sending continuous K28.7s, after 100,000 samples measured at the cross point of differential outputs, time referenced to REFCLKx± input, over the

operating range.

31. Total jitter is calculated at an assumed BER of 1E -12. Hence: Total Jitter (tJ) = (tRJ * 14) + tDJ.

32. Also meets all Jitter Generation and Jitter Tolerance requirements as specified by SMPTE 259, SMPTE 292, ESCON, FICON, Fibre Channel, and DVB-ASI.

CYV15G0404DXB AC Electrical Characteristics

(continued)

Parameter

Description

Min.

Max

Unit