Cypress Z9973 User Manual

3v, 125-mhz, multi-output zero delay buffer, Z9973, Features

3.3V, 125-MHz, Multi-Output Zero Delay Buffer

Z9973

Cypress Semiconductor Corporation

•

3901 North First Street

•

San Jose

•

CA 95134

•

408-943-2600

Document #: 38-07089 Rev. *D

Revised December 21, 2002

Features

• Output frequency up to 125 MHz

• 12 clock outputs: frequency configurable

• 350 ps max output-to-output skew

• Configurable output disable

• Two reference clock inputs for dynamic toggling

• Oscillator or PECL reference input

• Spread spectrum-compatible

• Glitch-free output clocks transitioning

• 3.3V power supply

• Pin-compatible with MPC973

• Industrial temperature range: –40°C to +85°C

• 52-pin TQFP package

Note:

1.

x = the reference input frequency, 200 MHz < F

VCO

< 480 MHz.

.

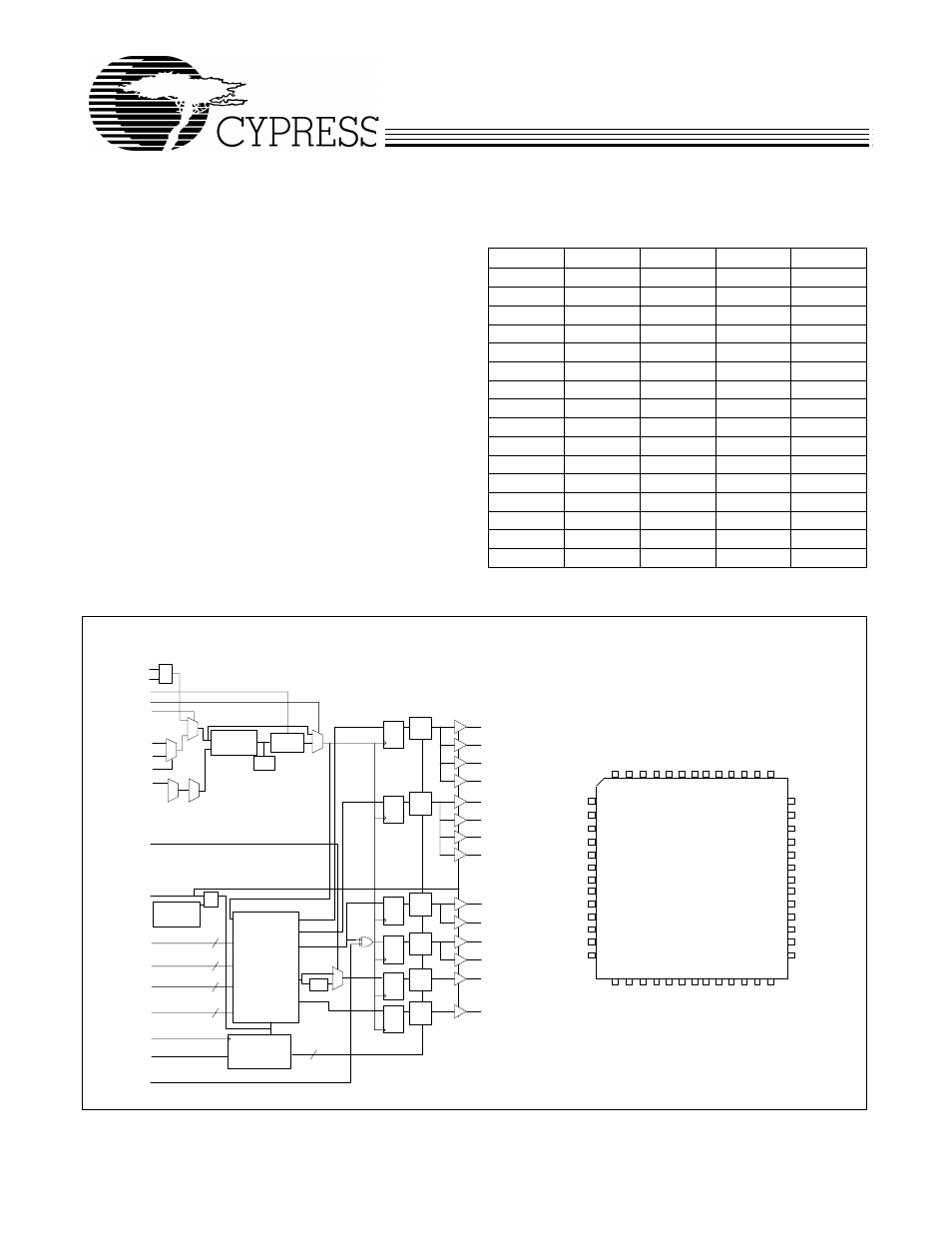

Table 1. Frequency Table

[1]

VC0_SEL

FB_SEL2

FB_SEL1

FB_SEL0

F

VC0

0

0

0

0

8x

0

0

0

1

12x

0

0

1

0

16x

0

0

1

1

20x

0

1

0

0

16x

0

1

0

1

24x

0

1

1

0

32x

0

1

1

1

40x

1

0

0

0

4x

1

0

0

1

6x

1

0

1

0

8x

1

0

1

1

10x

1

1

0

0

8x

1

1

0

1

12x

1

1

1

0

16x

1

1

1

1

20x

Block Diagram

Pin Configuration

REF_SEL

0

1

0

1

Phase

Detector

VCO

LPF

Sync

Frz

D Q

QA0

Sync

Frz

D Q

Sync

Frz

D Q

Sync

Frz

D Q

Sync

Frz

D Q

Sync

Frz

D Q

0

1

/2

Power-On

Reset

Output Disable

Circuitry

Data Generator

/4, /6, /8, /12

/4, /6, /8, /10

/2, /4, /6, /8

/4, /6, /8, /10

Sync Pulse

PECL_CLK

PECL_CLK#

TCLK0

TCLK1

TCLK_SEL

FB_IN

FB_SEL2

MR#/OE

SELA(0,1)

2

SELB(0,1)

2

SELC(0,1)

2

FB_SEL(0,1)

2

SCLK

SDATA

INV_CLK

QA1

QA2

QA3

QB0

QB1

QB2

QB3

QC0

QC1

QC2

QC3

FB_OUT

SYNC

12

VCO_SEL

PLL_EN

VSS

MR#/OE

SCLK

SDATA

FB_SEL2

PLL_EN

REF_SEL

TCLK_SEL

TCLK0

TCLK1

PECL_CLK

PECL_CLK#

VDD

F

B

_

SEL

1

SYN

C

VS

S

QC0

V

DDC

QC1

SEL

C

0

SEL

C

1

QC2

V

DDC

QC3

VS

S

INV

_

CLK

SEL

B1

SEL

B0

SEL

A1

SEL

A0

QA

3

V

DDC

QA

2

VS

S

QA

1

V

DDC

QA

0

VS

S

VC

O

_

SEL

VSS

QB0

VDDC

QB1

VSS

QB2

VDDC

QB3

FB_IN

VSS

FB_OUT

VDDC

FB_SEL0

1

2

3

4

5

6

7

8

9

10

11

12

13

39

38

37

36

35

34

33

32

31

30

29

28

27

14 15 16 17 18 19 20 21 22 23 24 25 26

52 51 50 49 48 47 46 45 44 43 42 41 40

Z9973