6digilent epp interface, 7factory loaded user demo – Digilent 410-282P-KIT User Manual

Page 3

Cmod S6™ Reference Manual

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 3 of 4

6

Digilent EPP Interface

The Cmod S6 implements the Digilent EPP interface (DEPP) for 8-bit parallel data transfers between the FPGA and

a computer attached via the USB Micro connector. DEPP is based on a set of API’s available in the Adept 2 public

SDK, available from the Adept product page a

These APIs work in concert with firmware

running on the USB controller to provide a high-level software interface for transporting data between a PC and

the Cmod S6.

To use the DEPP interface, the host PC must use software built from the Adept SDK DEPP libraries, and the FPGA

has to be running a configuration that implements a DEPP controller. For a description of the DEPP library API,

refer to the “DEPP Programmer's Reference Manual” included with the Adept 2 SDK. For information on designing

a DEPP controller, refer to the “Digilent Asynchronous Parallel Interface (DEPP)” document, also included with the

Adept 2 SDK.

7

Factory Loaded User Demo

The Quad SPI Flash is loaded with a configuration file at the factory. When powered on, the file will configure the

FPGA such that the buttons control the states of two LEDs, while the other two LEDs toggle at a speed of about 1

Hz. The general purpose I/O pins are initially configured as inputs, and are pulled up internally by the FPGA to read

a logic level ‘1’. Each individual pin can be controlled using the DEPP interface to either drive the pin as an output,

or to read the logic level that is present on the pin as an input.

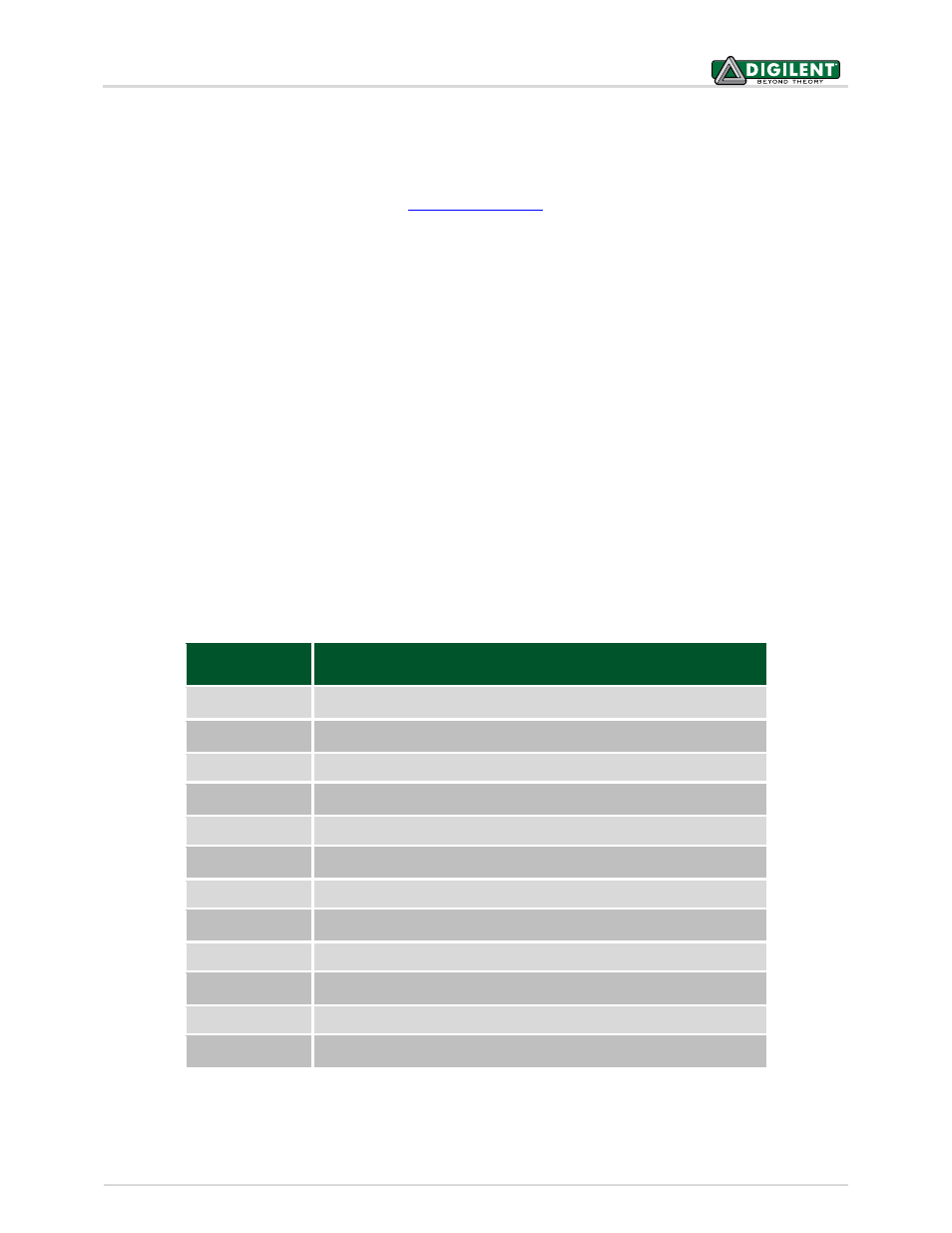

The I/O pins can be controlled by writing to specific DEPP register addresses. To test the interface, the “Register

I/O” tab within the Adept 2 application can be used. Table 1, shown below, gives a description of register

addresses and functions.

Address (HEX

value)

Function

0 (0x0)

Stores the logic value present on pins 1 through 8

1 (0x1)

Stores the logic value present on pins 9 through 16

2 (0x2)

Stores the logic value present on pins 17 through 23

3 (0x3)

Stores the logic value present on pins 26 through 33

4 (0x4)

Stores the logic value present on pins 34 through 41

5 (0x5)

Stores the logic value present on pins 42 through 48

6 (0x6)

Controls the I/O state of pins 1 through 8

7 (0x7)

Controls the I/O state of pins 9 through 16

8 (0x8)

Controls the I/O state of pins 17 through 23

9 (0x9)

Controls the I/O state of pins 26 through 33

10 (0xA)

Controls the I/O state of pins 34 through 41

11 (0xB)

Controls the I/O state of pins 42 through 48

Table 1. DEPP Register Map for factory loaded configuration.

The least significant bit in any register corresponds to the smallest pin number that it controls. Registers 6 through

11 will set up a pin controlled by registers 0 through 5 as an input if the corresponding bit in the register is a logic