Kontron COMe Eval Carrier QorIQ User Manual

Page 13

www.kontron.com

13

Quick Start Guide

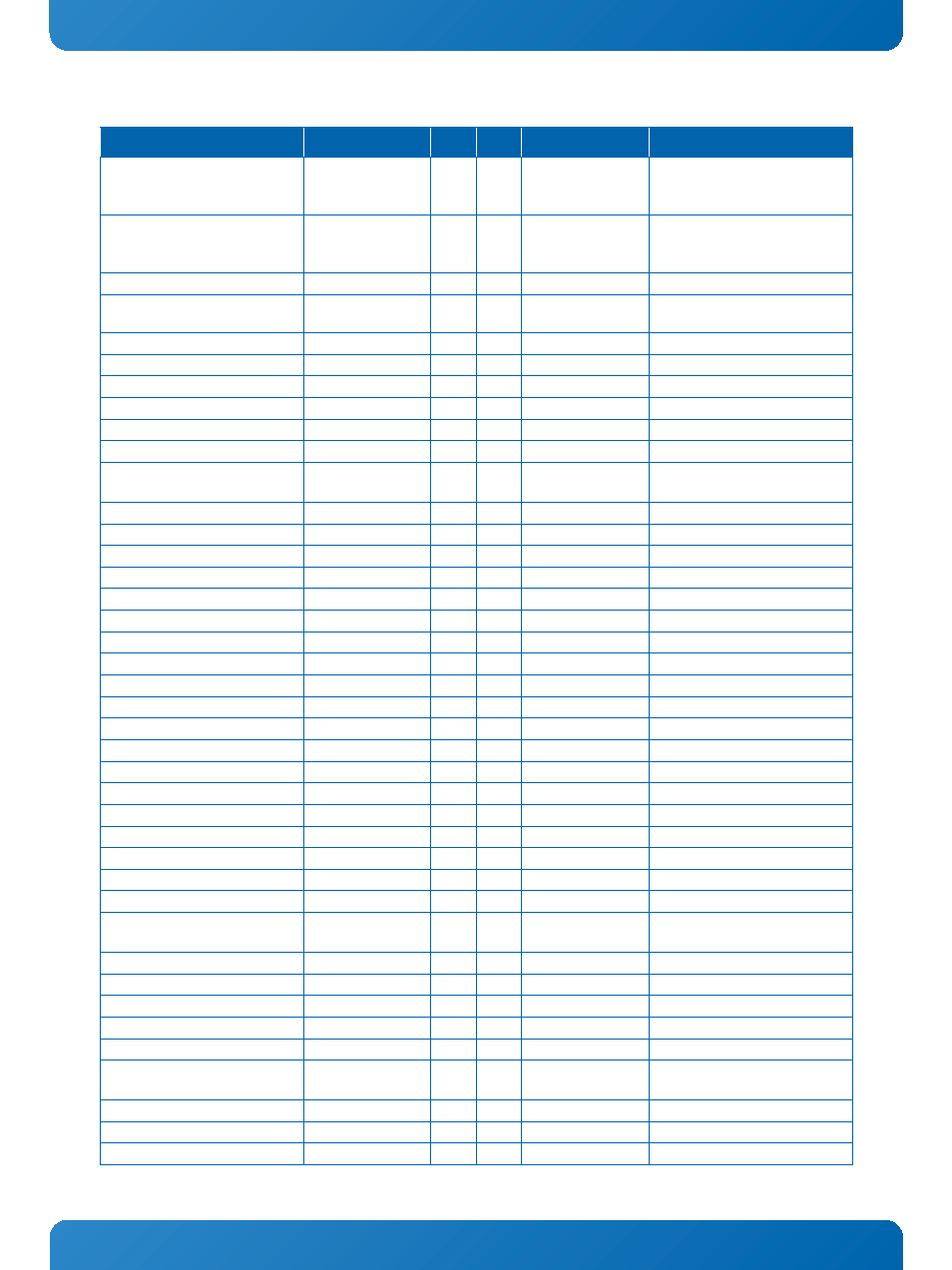

COME-QEC-1

Ethernet Management Clock for

SGMII PHY; routed to slot side-

band connector J23

EMI1_MDC

C47

D47

IRQ4# / GPIO

connected to carrier logic (not

actually used) and J26

Ethernet Management In/Out

for SGMII PHY; routed to slot

sideband connector J23

EMI1_MDIO

C48

D48

LA29

accessible via J22

accessible via J37

IRQ1# / GPIO

C49

D49

LA28

accessible via J22

accessible via J37

IRQ2# / GPIO

C50

D50

IRQ_OUT#

connected to carrier logic and

connector J37

GND

C51

D51

GND

accessible via J27

SERDES_RX8+

C52

D52

SERDES_TX8+

accessible via J27

accessible via J27

SERDES_RX8-

C53

D53

SERDES_TX8-

accessible via J27

T YPE0#

C54

D54

Reserved

accessible via J27

SERDES_RX9+

C55

D55

SERDES_TX9+

accessible via J27

accessible via J27

SERDES_RX9-

C56

D56

SERDES_TX9-

accessible via J27

T YPE1#

C57

D57

T YPE2#

connected to carrier logic (with

weak pullup)

accessible via J19

SERDES_RX10+

C58

D58

SERDES_TX10+

accessible via J19

accessible via J19

SERDES_RX10-

C59

D59

SERDES_TX10-

accessible via J19

GND

C60

D60

GND

accessible via J19

SERDES_RX11+

C61

D61

SERDES_TX11+

accessible via J19

accessible via J19

SERDES_RX11-

C62

D62

SERDES_TX11-

accessible via J19

accessible via J22

LA25

C63

D63

LA27

accessible via J22

accessible via J22

LA24

C64

D64

LA26

accessible via J22

accessible via J19

SERDES_RX12+

C65

D65

SERDES_TX12+

accessible via J19

accessible via J19

SERDES_RX12-

C66

D66

SERDES_TX12-

accessible via J19

accessible via J22

LA23

C67

D67

GND

accessible via J19

SERDES_RX13+

C68

D68

SERDES_TX13+

accessible via J19

accessible via J19

SERDES_RX13-

C69

D69

SERDES_TX13-

accessible via J19

GND

C70

D70

GND

accessible via J20

SERDES_RX14+

C71

D71

SERDES_TX14+

accessible via J20

accessible via J20

SERDES_RX14-

C72

D72

SERDES_TX14-

accessible via J20

GND

C73

D73

GND

accessible via J20

SERDES_RX15+

C74

D74

SERDES_TX15+

accessible via J20

accessible via J20

SERDES_RX15-

C75

D75

SERDES_TX15-

accessible via J20

GND

C76

D76

GND

accessible via J22

LA22

C77

D77

IRQ5# / GPIO

connected to carrier logic (not

actually used) and J37

accessible via J20

SERDES_RX16+

C78

D78

SERDES_TX16+

accessible via J20

accessible via J20

SERDES_RX16-

C79

D79

SERDES_TX16-

accessible via J20

GND

C80

D80

GND

accessible via J20

SERDES_RX17+

C81

D81

SERDES_TX17+

accessible via J20

accessible via J20

SERDES_RX17-

C82

D82

SERDES_TX17-

accessible via J20

accessible via J22

LA21

C83

D83

T YPE3#

connected to carrier logic (with

weak pullup)

GND

C84

D84

GND

N/C

C85

D85

N/C

N/C

C86

D86

N/C

Table 3: Connector J2 Rows C and D Pinout (Continued)

COMMENT

SIGNAL

PIN

PIN

SIGNAL

COMMENT