Xg_lanelinx details, Lanelinx2p5g, Link_fsm – Achronix Speedster22i LaneLinx User Manual

Page 5

UG035 (v1.0), March 19, 2012

5

XG_Lanelinx Details

LaneLinx2p5g:

This block is the instantiation of the Hard SerDes IP contained within the Speedster22i Frame. For the

included example implementation we have already created a 2.5 Gbps SerDes Macro. To change the

data rate, a new SerDes Macro can be generated using the ACE IP Generator GUI. If a new macro is

generated, it can simply be used as a drop in replacement for the existing one.

The Key internal signals from the SerDes macros are

•

lane0_o_pma_sig_detect

•

lane0_o_pma_txready

•

lane0_o_pma_rxready

•

lane0_o_pma_synthready

•

lane0_o_rx_data_clk

•

laneo_o_tx_data_clk

•

lane0_o_rx_syma_locked

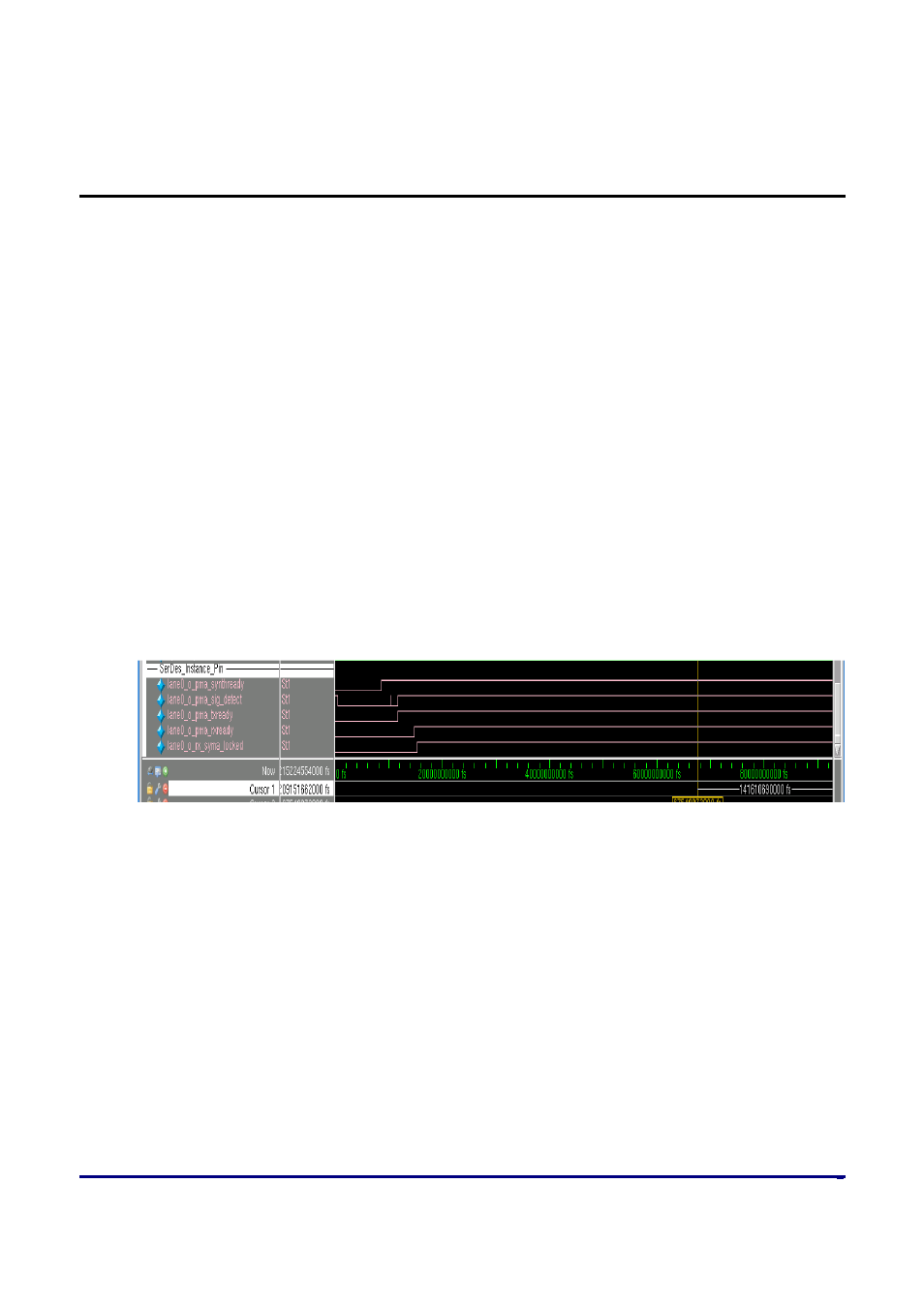

Figure 2 below shows how the Speedster22i SerDes pins should be asserted during correct start up

Figure 2 – Correct operation of SerDes pins

The “Link_FSM” block will respond based on the value of these signals

Link_FSM:

This is the main control block for implementing the LaneLinx protocol. This controls data flow based

on incoming data (in both the TX and RX directions) as well as based on the status of the Key SerDes

signals:

•

lane0_o_pma_sig_detect

•

lane0_o_pma_txready

•

lane0_o_pma_rxready

•

lane0_o_pma_synthready

•

lane0_o_rx_data_clk

•

lane0_o_tx_data_clk

•

lane0_o_rx_syma_locked